Familia Renesas RA de microcontrolere bazate pe Arm Cortex continuă istoria bogată a microcontrolerelor Renesas care au apărut înainte, cum ar fi popularele familii H8 sau M16C. Familia RA utilizează sau îmbunătățește multe dintre funcțiile periferice implementate inițial pe aceste dispozitive. Toate aceste periferice au fost încercate și testate de-a lungul multor ani și asigură o operare dovedită și previzibilă. Unele oferă, de asemenea, caracteristici unice care pot îmbunătăți performanța unei aplicații sau pot reduce consumul de putere al acesteia.

Familia Renesas RA de microcontrolere bazate pe Arm Cortex continuă istoria bogată a microcontrolerelor Renesas care au apărut înainte, cum ar fi popularele familii H8 sau M16C. Familia RA utilizează sau îmbunătățește multe dintre funcțiile periferice implementate inițial pe aceste dispozitive. Toate aceste periferice au fost încercate și testate de-a lungul multor ani și asigură o operare dovedită și previzibilă. Unele oferă, de asemenea, caracteristici unice care pot îmbunătăți performanța unei aplicații sau pot reduce consumul de putere al acesteia.

În acest articol, vom examina cum funcționează unele dintre aceste periferice și cum pot fi combinate pentru a automatiza multe dintre sarcinile de nivel scăzut care trebuie gestionate într-o aplicație tipică bazată pe microcontroler.

Probabil că unul dintre cele mai interesante – dar mai puțin înțelese – periferice din interiorul unui microcontroler RA, tipic, este circuitul de operare a datelor (DOC – Data Operations Circuit). Acesta poate oferi avantaje semnificative legate de performanță în aplicații în timp real, permițând transferarea unor sarcini simple de la CPU. Acest aspect îmbunătățește timpul de răspuns și poate reduce consumul de putere. Este valabil mai ales atunci când DOC este utilizat împreună cu unele dintre celelalte caracteristici mai avansate disponibile pe familia RA.

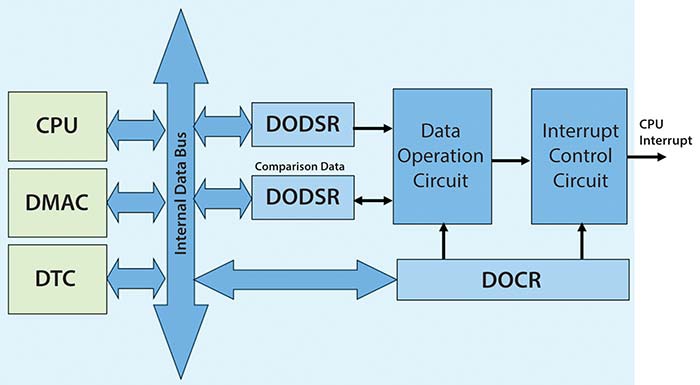

În centrul DOC se află o unitate logică aritmetică simplă (ALU – Arithmetic Logic Unit). Această ALU simplă are doar trei funcții de bază: poate face o comparație de date pe 16-biți, o adunare pe 16-biți sau o scădere pe 16-biți și apoi poate genera o întrerupere bazată pe o anumită condiție de ieșire. Toate aceste funcții pot fi executate fără nicio intervenție din partea CPU. Acest lucru se realizează prin transferul automat al datelor care urmează să fie operate de DOC, folosind fie un controler de acces direct la memorie (DMAC – Direct Memory Access Controller), fie un controler de transfer de date, pe care le vom explica în cele ce urmează. Vedeți figura 1.

Atunci când se utilizează modul de comparare pe 16-biți, o valoare de referință inițială este încărcată în DOC. Datele pe 16-biți care urmează să fie comparate sunt apoi încărcate și comparate cu valoarea de referință în hardware. DOC poate fi programat să genereze o întrerupere la o potrivire adevărată sau falsă.

Atunci când se utilizează modul de adunare pe 16-biți, o valoare inițială pe 16-biți este încărcată în DOC. Valori suplimentare pe 16-biți sunt apoi încărcate (una sau mai multe) în DOC și sunt adăugate la valoarea inițială. Atunci când sunt încărcate toate valorile necesare, se verifică dacă există o depășire a numărului de valori și se generează o întrerupere, dacă este necesar. Acest mecanism simplu permite luarea unei decizii în cazul în care o anumită valoare de prag a fost depășită, ideal, de exemplu, pentru detectarea automată a nivelului cu ajutorul ADC-ului.

Atunci când se utilizează modul de scădere pe 16-biți, se încarcă în DOC o valoare inițială pe 16-biți. Valori suplimentare pe 16-biți sunt apoi încărcate (din nou, pot fi una sau mai multe) în DOC și sunt scăzute din valoarea inițială. Atunci când sunt încărcate toate valorile necesare, se verifică dacă nu se înregistrează o depășire a debitului și se generează o întrerupere, dacă este necesar. Acest mecanism simplu permite, din nou, luarea unei decizii dacă a fost depășită o anumită valoare de prag.

Cu toate acestea, adevărata putere a circuitului de operare a datelor constă în faptul că aceste trei funcții simple pot fi utilizate pentru a lua decizii cu privire la felul în care ar trebui să funcționeze sistemul. Acest lucru înseamnă că putem interveni direct în hardware-ul microcontrolerului, permițând acestuia să decidă cum să răspundă la date de intrare specifice.

Atunci când DOC este combinat cu periferice cum ar fi controlerul DMA sau controlerul de transfer de date (DTC), care pot automatiza transmiterea datelor către DOC, putem vedea cum poate fi folosit pentru a crea un sistem capabil să ia decizii pe baza datelor provenite, aproape, din orice sursă. Această operațiune poate fi realizată fără nicio intervenție a CPU, chiar și atunci când CPU se află în stare de somn. Acest lucru poate oferi un răspuns mult mai rapid la schimbarea datelor, mai degrabă decât să aștepte ca CPU să poată interveni pentru a răspunde apoi la eveniment.

Ne putem imagina multe cazuri în care DOC ar putea fi utilizat. Un exemplu este convertorul analogic-digital (ADC) dintr-un sistem de detectare a nivelului pentru a detecta automat când nivelul depășește un prag programat. Utilizarea DOC pentru astfel de funcții prezintă numeroase avantaje. De exemplu, unitatea centrală de procesare ar putea fi dedicată altor sarcini cu prioritate ridicată și ar putea fi alertată de o întrerupere DOC doar atunci când este atinsă o anumită condiție de intrare. Unitatea centrală de procesare poate fi plasată în stare de somn pentru a reduce consumul de putere și poate fi trezită din nou doar de o întrerupere la o condiție de alarmă validă detectată de DOC.

Circuitul de operare a datelor este disponibil pe toți membrii familiei RA. Renesas a continuat să îmbunătățească DOC, iar cele mai recente versiuni au funcții suplimentare, permițând luarea unor decizii și mai complexe asupra datelor.

Să ne uităm acum la Controlerul de transfer de date (DTC) pe care l-am menționat mai devreme. Acesta este un periferic care a fost proiectat pentru a oferi un mecanism simplu, dar extrem de flexibil, de transfer de date între un periferic și memorie sau între memorie și un periferic. Un controler de transfer de date poate fi găsit pe toți membrii familiei de microcontrolere RA.

DTC utilizează un controler simplu programabil pentru a efectua aceste transferuri, păstrând informațiile de configurare într-un tabel din SRAM. Acesta este mult mai mic decât utilizarea unui bloc hardware mare, dedicat pentru această sarcină, cum este utilizat, de obicei, de către controlerul DMA. Datorită acestei programabilități, se obține un nivel mult mai mare de flexibilitate în comparație cu utilizarea unui DMAC. Prin stocarea în SRAM a tabelului de configurare care descrie transferul, putem avea canale aproape nelimitate, restricționate doar de cantitatea de SRAM disponibilă.

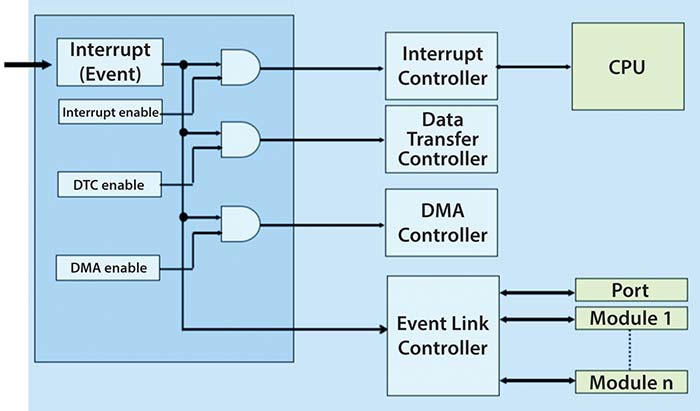

La familia RA, un eveniment (sau întrerupere) declanșat de CPU, un periferic sau un pin extern pot genera mai multe acțiuni pe dispozitiv. Figura 2 prezintă o diagramă simplificată a controlerului de întreruperi. În ea se ilustrează modul în care un eveniment poate declanșa mai multe acțiuni. Acestea includ o întrerupere tradițională, care modifică fluxul de program al aplicației; un transfer DMAC; sau un transfer DTC. Este, de asemenea, posibil să se declanșeze mai multe dintre aceste acțiuni, de la un singur eveniment.

Așadar, să analizăm în detaliu DTC-ul. Utilizând SRAM pentru a păstra informațiile de configurare DTC, controlerul DTC poate fi folosit pentru a crea nu doar unul sau două canale de transfer de date, ci 10, 20 sau chiar mai multe, dacă este necesar. Principalul dezavantaj al acestui mecanism este că, pentru fiecare transfer, trebuie efectuate câteva cicluri pentru a citi datele de configurare păstrate în SRAM înainte de fiecare transfer. Ca urmare, transferul DTC este, în general, mai lent decât un transfer DMA.

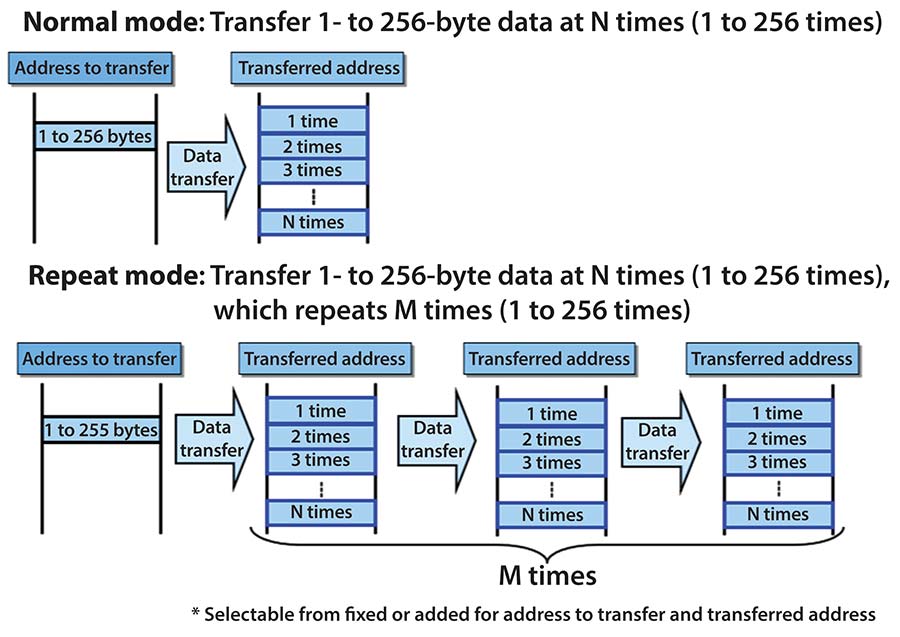

DTC poate transfera 1 octet sau mai mult, între un periferic și memorie sau între memorie și periferic, de până la 256 de ori. Adresele de sursă și de destinație pentru transfer pot fi identice sau pot fi incrementate sau decrementate independent, creând astfel o structură tampon în memorie.

La sfârșitul transferului, DTC poate genera o întrerupere pentru a anunța CPU că datele sunt gata sau poate declanșa un al doilea transfer DTC. Acest lucru poate fi utilizat pentru a înlănțui mai multe transferuri, motiv pentru care este cunoscut sub numele de “chain mode”. Modul înlănțuit poate fi deosebit de util în cazul în care este necesară deplasarea mai multor părți de date între periferice și memorie. ‘Chain mode’ este deosebit de interesant atunci când este utilizat cu DOC despre care am discutat anterior, deoarece aceasta înseamnă că mai multe transferuri din diferite locații din memorie și/sau de la un periferic pot fi declanșate de o singură sursă de întrerupere. Ceea ce rezultă, de exemplu, este că prin intermediul unei singure întreruperi, cum ar fi întreruperea ADC, putem provoca încărcarea datelor de comparație în DOC. Prin înlănțuirea unui al doilea transfer, putem încărca DOC cu datele de la ADC pentru a fi comparate, totul fiind complet automat. Această abilitate a unei singure întreruperi de a genera o secvență complexă de transferuri diferite este extrem de puternică, nu numai atunci când este utilizată cu DOC. Unele dintre diferitele moduri de operare ale DTC sunt prezentate în figura 3.

DTC poate fi, de asemenea, plasat în modul de repetare, în care va repeta transferul de un număr suplimentar de ori. Pentru majoritatea aplicațiilor, flexibilitatea DTC oferă un compromis perfect între viteză și flexibilitate. Utilizatorii pot crea transferuri automate între orice periferic și memorie, aproape fără limite.

Acest lucru demonstrează cum poate fi DTC mult mai flexibil decât controlerul DMA tradițional. DMAC este în continuare o metodă mai rapidă dacă sunt necesare cele mai mari viteze de transfer de date și aproape toate microcontrolerele RA includ un număr de canale DMAC. Cu toate acestea, pentru flexibilitate și gestionarea ușoară a datelor, DTC câștigă detașat. În plus, utilizatorii pot crea mai multe canale, limitate doar de SRAM-ul disponibil.

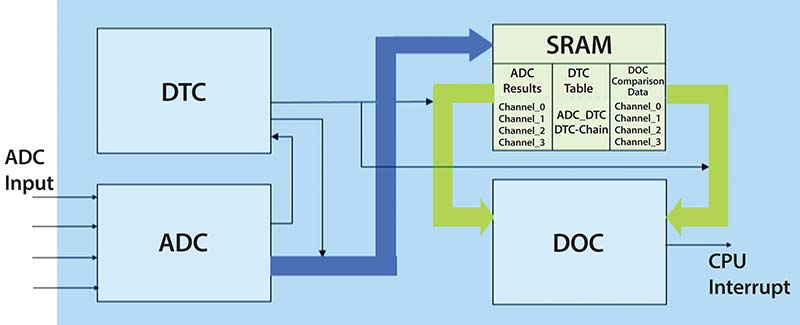

Să analizăm acum modul în care DTC și DOC pot fi combinate cu ADC-ul pentru a crea un sistem inteligent de eșantionare analogică. Potențial, acest lucru reduce solicitarea asupra CPU și chiar contribuie la scăderea consumului de putere, punând CPU în stare de somn în timp ce ADC, DTC și DOC funcționează. Sistemul pe care dorim să îl creăm este un detector simplu de nivel cu intrări multiple, care utilizează modul de scanare în grup al ADC-ului pe 12-biți pentru a eșantiona, pe rând, fiecare dintre cele 4 semnale de intrare. Folosind combinația dintre DTC și DOC, acesta detectează dacă este depășit un nivel de prag programabil.

Sistemul va genera o întrerupere și va trezi CPU doar dacă această valoare a fost depășită.

După configurarea inițială a sistemului, CPU intră în stare de somn pentru a economisi energie și se trezește numai dacă apare o întrerupere de la DOC, indicând că pragul a fost depășit. O schemă simplificată a sistemului este prezentată în figura 4.

În modul de scanare de grup, ADC eșantionează continuu fiecare intrare în parte și copiază rezultatul în SRAM. Când toate cele 4 intrări au fost eșantionate, ADC-ul generează o cerere DTC. Utilizând ‘chain mode’, această cerere inițiază un lanț de 8 transferuri între memorie și DOC. Din SRAM pe cip, se copiază atât rezultatele celor 4 ADC-uri, cât și o valoare de prag corespunzătoare cu care trebuie comparat fiecare rezultat ADC.

Cerere de transfer ADC către DTC.

DTC transfer 1 Comparație[0] la DOC. Chain Activat, deci se realizează următorul transfer

DTC transfer 2 AN000 la DOC Chain Activat, deci se realizează următorul transfer

DTC transfer 3 Comparație[0] la DOC Chain Activat, deci se realizează următorul transfer

DTC transfer 4 AN001 la DOC Chain Activat, deci se realizează următorul transfer

DTC transfer 5 Comparație[0] la DOC Chain Activat, deci se realizează următorul transfer

DTC transfer 6 AN003 la DOC Chain Activat, deci se realizează următorul transfer

DTC transfer 7 Comparație[0] la DOC Chain Activat, deci se realizează următorul transfer

DTC transfer 8 AN005 la DOC Chain Dezactivat, așadar stop

În acest caz, inițializăm DOC pentru a compara fiecare valoare și a genera o întrerupere dacă oricare dintre valorile de prag este depășită.

Odată ce ADC, DOC și DTC sunt inițializate, fiecare intrare ADC este verificată continuu “în spate” (background). Procesorul poate gestiona alte sarcini sau poate fi plasat în stare de somn și nu se va trezi până când una dintre intrări nu depășește valoarea relevantă.

Multe alte sarcini de nivel scăzut pot fi automatizate prin combinarea DOC și DTC în același mod. Aceasta poate fi o tehnică extrem de puternică de automatizare a funcțiilor de nivel scăzut. Ea poate economisi timp și costuri de dezvoltare pentru crearea de drivere software de nivel scăzut, precum și pentru îmbunătățirea performanțelor sistemului.

Fiecare membru al familiei de microcontrolere RA include funcții periferice inteligente, cum ar fi Circuitul de operare a datelor și Controlerul de transfer de date, împreună cu multe alte funcții periferice de putere care pot fi, de asemenea, utilizate pentru a crea subsisteme inteligente. Împreună, DOC și DTC oferă soluții extrem de flexibile și puternice pentru automatizarea funcțiilor I/O de nivel scăzut în numeroase și diferite aplicații. Automatizarea acestor funcții de nivel scăzut nu numai că îmbunătățește timpul de răspuns al sistemului la evenimente în timp real, dar poate reduce, de multe ori, complexitatea și dimensiunea software-ului de sistem. În acest fel, crește fiabilitatea și se reduc costurile de testare a sistemului.

Familia de microcontrolere RA este destinată unei game largi de aplicații de comunicații și control, cum ar fi controlul motoarelor, senzori inteligenți, contorizare, instrumente portabile, modemuri de mică putere și multe alte aplicații industriale și de consum. Este disponibilă într-o gamă largă de opțiuni de dimensiuni ale memoriei și de capsule. Pentru mai multe informații, vizitați www.renesas.com/ra.

![]() Autor:

Autor:

Graeme Clark

Principal Engineer

Renesas Electronics Europe | https://www.renesas.com

![]()