Acest articol oferă o discuție aprofundată a conceptului de nivel înalt al salturilor de frecvență (FH), a principiilor de proiectare ale FH activate prin arhitectura flexibilă a buclei de prindere a fazei (PLL) a transceiverului SDR ADRV9002 și a celor patru caracteristici FH majore ale acestuia. Asemenea caracteristici permit utilizatorilor să dispună de capabilitățile FH pentru a face față unor aplicații precum Link 16 și încărcarea rapidă în timp real a frecvenței purtătoare atât în modurile de operare cu un singur canal, cât și cu două canale. În plus, combinația FH cu sincronizarea multichip (MCS) și predistorsionarea digitală (DPD) face din acest transceiver SDR o soluție atractivă pentru realizarea cerințelor avansate din sistemele de comunicații complexe de astăzi.

Acest articol oferă o discuție aprofundată a conceptului de nivel înalt al salturilor de frecvență (FH), a principiilor de proiectare ale FH activate prin arhitectura flexibilă a buclei de prindere a fazei (PLL) a transceiverului SDR ADRV9002 și a celor patru caracteristici FH majore ale acestuia. Asemenea caracteristici permit utilizatorilor să dispună de capabilitățile FH pentru a face față unor aplicații precum Link 16 și încărcarea rapidă în timp real a frecvenței purtătoare atât în modurile de operare cu un singur canal, cât și cu două canale. În plus, combinația FH cu sincronizarea multichip (MCS) și predistorsionarea digitală (DPD) face din acest transceiver SDR o soluție atractivă pentru realizarea cerințelor avansate din sistemele de comunicații complexe de astăzi.

Introducere

Spre deosebire de comunicațiile radio convenționale, saltul de frecvență (FH) definește o metodă de transmitere a semnalelor radio prin schimbarea rapidă a frecvenței purtătoare1), fiind menționată pentru prima dată de Nikola Tesla în brevetul său american din 1903, “Method of Signaling”. Mai târziu, în 1942, actrița Hedy Lamarr și compozitorul George Antheil au consolidat conceptul prin utilizarea unui rulou de pian pentru a sincroniza schimbările între cele 88 de frecvențe (n.red.: nu întâmplător, acesta este și numărul standard de clape ale pianului) cu scopul de a preveni interferențele provocate de controlul radio al torpilelor. În ultimii o sută de ani, de la comunicațiile în timp nereal și cu viteză redusă între punctele de comandă fixe din Primul Război Mondial până la comunicațiile multimedia în timp real și de mare viteză între avioane, nave și sisteme terestre, FH a ajuns într-o nouă eră a aplicațiilor militare. În plus, FH a fost adoptată pe scară largă în multe rețele de comunicații personale fără fir, cum ar fi Bluetooth® Personal Area Network (PAN), precum și în zonele de radiocomunicații pentru consumatori și pasionați, cum ar fi “walkie-talkie”, machete de mașini și drone.

Ce este saltul de frecvență?

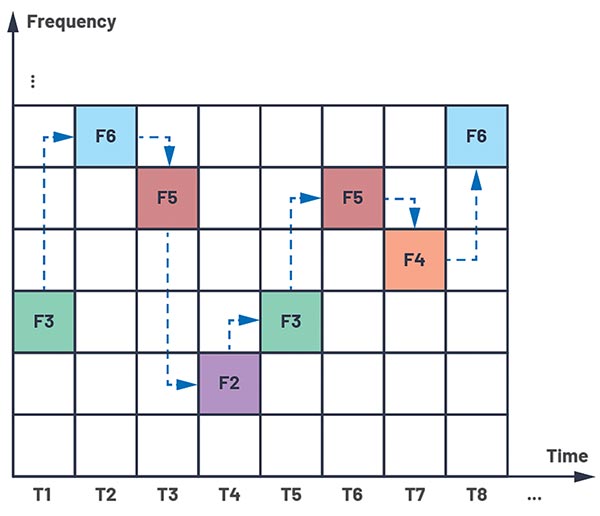

Conceptul de nivel înalt al FH este descris în figura 1. Întreaga bandă de frecvență și durata de timp sunt împărțite în grile bidimensionale. În orice interval de timp dat, o subbandă de frecvență diferită este utilizată pentru comunicații. Acest lucru prezintă avantajul unei rezistențe ridicate la interferențele în bandă îngustă și al unei capabilități puternice de combatere a interceptărilor rău intenționate și a bruiajului, deoarece caracterul aleatoriu al modelului de salt adaugă în mod echivalent un alt nivel de securitate care poate fi decodificat numai între emițător și receptor. În plus, semnalele FH pot împărți cu ușurință lățimea de bandă cu alte comunicații convenționale datorită interferențelor reciproce minime, ceea ce duce la o eficiență ridicată a spectrului. Cu o rată de salt mai mare și un set mai mare de subbenzi de frecvență, avantajele FH devin mai importante, ceea ce face din ea o soluție atractivă pentru diverse aplicații.

Următoarea generație de transceivere SDR

ADRV9002 este un emițător-receptor SDR dual de bandă îngustă și de bandă largă, care oferă performanțe RF de ultimă generație, precum și caracteristici avansate de sistem, cum ar fi DPD și FH. ADRV9002 operează de la 30 MHz la 6 GHz și acoperă benzile de frecvență ultraînaltă (UHF); benzile de frecvență foarte înaltă (VHF); benzile industriale, științifice și medicale (ISM); și benzile de frecvență celulară în bandă îngustă (kHz) și bandă largă până la 40 MHz. Figura 2 prezintă o schemă bloc de nivel înalt a ADRV9002. Acesta include canale duble de transmisie și recepție cu un set de algoritmi avansați de procesare digitală a semnalelor. Structura PLL evidențiată cu roșu este unică în sensul că, în loc să aibă un circuit PLL dedicat pentru calea de date de recepție și unul pentru calea de date de transmisie, așa cum au multe alte transceivere, în dispozitiv sunt utilizate două circuite PLL RF, acestea putând “alimenta” opțional orice receptor sau emițător, sau ambele, sau niciunul. Această flexibilitate este esențială pentru a susține FH în diverse aplicații TDD, cum ar fi operațiunile cu un singur canal și cu două canale, inclusiv în modul de numai emisie (1T/2T), în modul de numai recepție (1R/2R) și în modul de emisie și recepție (1T1R/2T2R). Atât diversitatea canalelor, cât și multiplexarea canalelor sunt acceptate pentru funcționarea cu două canale. În plus, două PLL-uri pot fi operate în modul “ping pong” pentru a satisface cerințele stricte de sincronizare FH.

Patru caracteristici FH majore ale ADRV9002

FH foarte rapid prin multiplexarea a două circuite PLL și resincronizarea rapidă a acestora

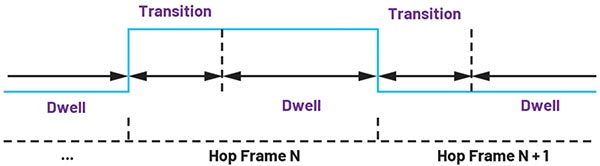

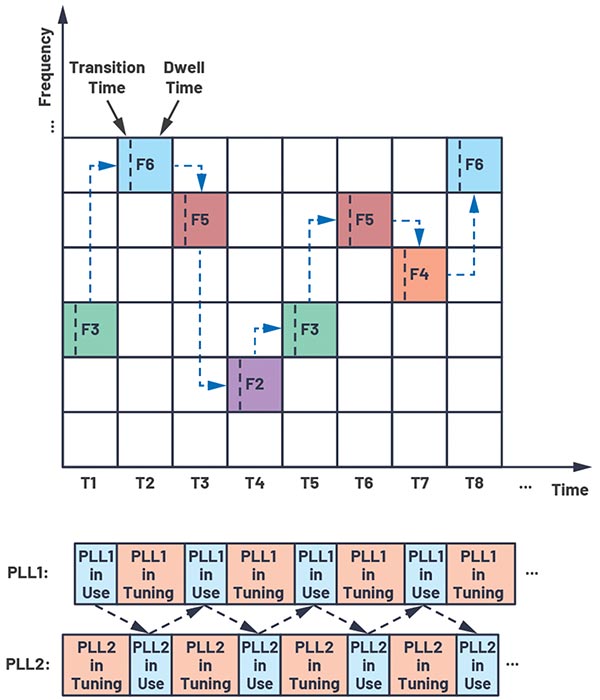

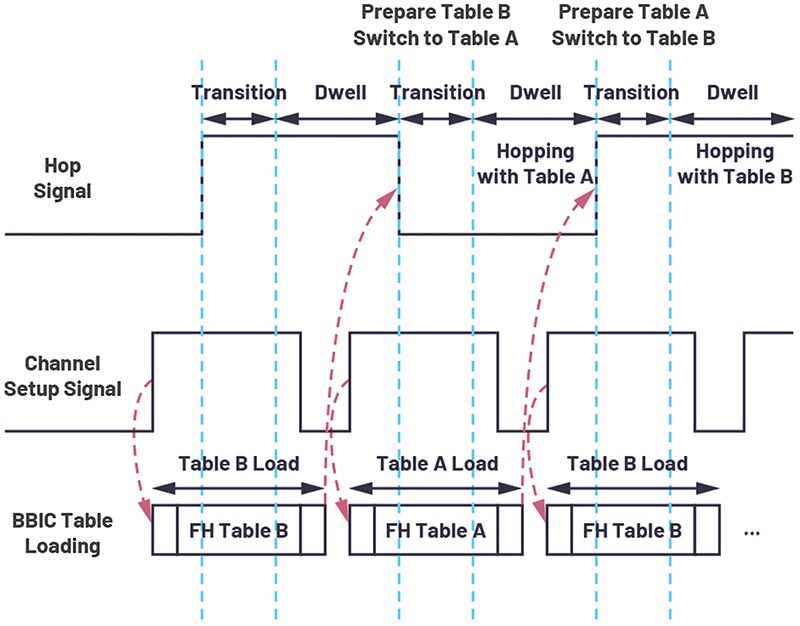

FH se obține prin resincronizarea (reajustarea) circuitului PLL înainte de trecerea la o frecvență diferită. ADRV9002 oferă diferite moduri FH în funcție de utilizarea circuitului PLL.2) Fiecare interval de timp din figura 1 reprezintă un interval de timp de salt, care este împărțit într-o perioadă de tranziție și o perioadă de așteptare, după cum se arată în figura 3.

Într-un mod FH mai lent, cu un timp de tranziție suficient de lung (mai mare decât timpul de configurare a canalului și timpul de sincronizare PLL necesar) între schimbările de frecvență, este necesar un singur circuit PLL pentru o pereche de canale de transmisie și recepție într-o operațiune TDD (modul de resincronizare PLL). Pentru a obține un FH mai rapid cu un timp de tranziție mai scurt (mai scurt decât timpul de configurare a canalului și timpul de ajustare PLL necesar), în dispozitiv sunt utilizate două circuite PLL (modul “PLL mux”). Cele două PLL-uri se coordonează între ele în mod “ping-pong”: în timp ce un PLL este utilizat pentru frecvența curentă, celălalt PLL este reajustat pentru următoarea frecvență. Acest lucru face posibil un FH foarte rapid și ar putea reduce semnificativ timpul de tranziție necesar între diferite schimbări de frecvență. Aceste două moduri sunt rezumate în tabelul 1.

| Mod FH | Timp de tranziție | PLL-uri pentru o pereche de canale | Timp de resincronizare PLL autorizat |

| “PLL Mux” | <Timp de resincronizare PLL | Două PLL-uri | <Două tranziții + o pauză |

| Resincronizare PLL | >Timp de resincronizare PLL | Un PLL | <O singură tranziție |

Tabelul 1: Modul FH al ADRV9002 bazat pe utilizarea PLL-ului

După cum se arată în tabelul 1, selectarea acestor două moduri depinde de timpul de tranziție definit de utilizator.

Figura 4 descrie în continuare modul “PLL mux”. După cum s-a menționat mai devreme, fiecare interval de timp reprezintă un interval de timp de salt format dintr-o perioadă de tranziție și o perioadă de timp de așteptare. Atunci când un PLL este utilizat în timpul perioadei de așteptare (pauză), celălalt PLL începe să se ajusteze de la începutul timpului de tranziție al aceluiași interval de timp de salt. Acesta poate continua ajustarea până la sfârșitul perioadei de tranziție a următoarei secvențe de salt. Prin urmare, modul “PLL mux” are succes atâta vreme cât timpul de ajustare PLL necesar este mai mic decât suma unui timp de așteptare plus două perioade de tranziție.

FH în mod “PLL mux” este esențial pentru aplicațiile militare, cum ar fi Link 16. Acesta este considerat unul dintre cele mai importante standarde de linkuri de date tactice utilizate de NATO (North Atlantic Treaty Organization) ca un link de date digitale de mare viteză, rezistent la bruiaj, care funcționează în banda de frecvențe radio de la 960 MHz la 1,215 GHz.3) Prin calibrarea corectă a întregului interval de frecvență de salt la momentul inițializării, ADRV9002 utilizează modul de resincronizare rapidă a PLL pentru a îndeplini cerințele stricte de sincronizare. Timpul de reajustare PLL depinde de rata ceasului de referință PLL al ADRV9002. Tabelul 2 prezintă timpul necesar de resincronizare rapidă a PLL-ului pe baza unei rate diferite a ceasului de referință PLL. La o rată a ceasului de referință PLL de 300 MHz, timpul de resincronizare rapidă a PLL este de aproximativ 15 μs. Cu o lungime a frame-ului de salt de 13 μs pentru Link 16, timpul de resincronizare PLL de 15 μs − atunci când se utilizează modul “PLL mux” − poate satisface cerința de sincronizare dacă timpul de tranziție este mai mare de 2 μs, așa cum se arată în tabelul 1.

| Ceas de referință PLL (MHz) | Timp de resincronizare rapidă PLL (μs) |

| 30 | 91 |

| 38.4 | 77 |

| 50 | 56 |

| 100 | 27 |

| 150 | 21 |

| 200 | 20 |

| 250 | 17 |

| 300 | 15 |

Tabelul 2: Timpul de resincronizare PLL utilizând modul de resincronizare rapidă PLL

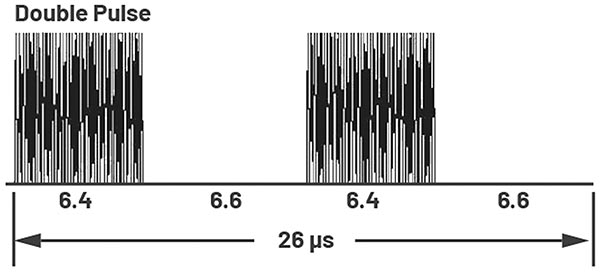

După cum se descrie în lucrarea de licență “Performance Analysis of a JTIDS/Link 16 Type Waveform Transmitted over Slow, Flat Nakagami Fading Channels in the Presence of Narrowband Interference”3), mesajul de date Link 16 poate fi trimis fie ca un singur impuls, fie ca un impuls dublu, în funcție de structura de împachetare. Structura cu un singur impuls constă într-un timp de activare de 6,4 μs și un timp de dezactivare de 6,6 μs, cu o durată totală de 13 μs. Structura dublu-impuls constă în două impulsuri simple care transportă aceleași date, dar utilizează frecvențe purtătoare diferite, așa cum se arată în figura 5. Prin urmare, timpul de tranziție ar putea fi de 6,6 μs (>2 μs), ceea ce face ca Link 16 FH să fie fezabil cu ADRV9002.

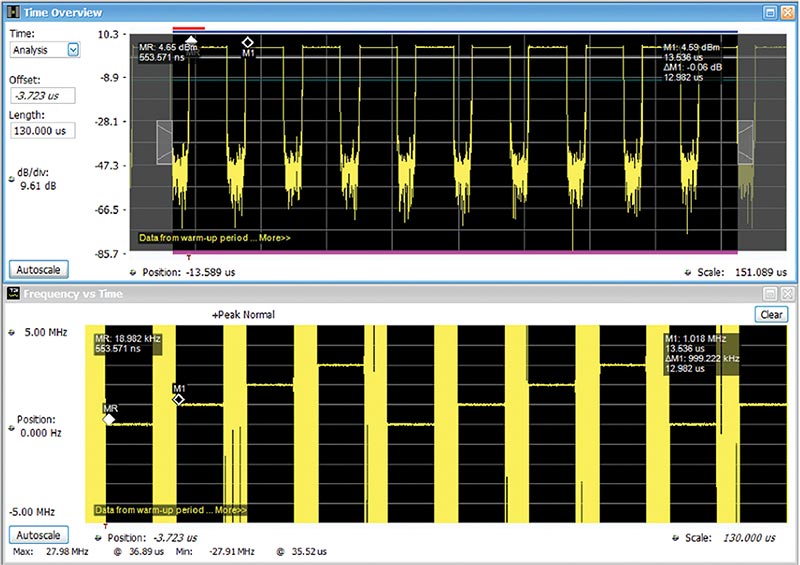

Figura 6 prezintă ieșirea transmisiei ADRV9002 (puterea în funcție de timp și frecvența în funcție de timp) cu frame-uri de salt de tip Link 16 (pentru simplificare se utilizează doar FH de transmisie). Rețineți că, pentru a evidenția timpul minim de tranziție pe care îl poate obține ADRV9002, experimentul nu urmează structura standard a pulsurilor Link 16 din figura 5.

Timpul de conectare este mărit de la 6,4 μs la 11 μs, iar timpul de deconectare este redus de la 6,6 μs la 2 μs. Un analizor de spectru Tektronix RSA306B este conectat la portul de ieșire de transmisie de pe placa de evaluare ADRV9002 pentru analiză. Graficul superior indică performanța puterii în funcție de timp. Se poate observa că saltul de transmisie are loc la fiecare 13 μs, cu un timp de tranziție de aproximativ 3 μs între cadrele consecutive de salt de transmisie. Graficul de jos ilustrează performanța frecvenței în funcție de timp. În acest experiment, frecvența purtătoarei de emisie trece prin patru frecvențe diferite cu un pas de 1 MHz. Așa cum era de așteptat, graficul de jos dovedește că ieșirea transmisiei trece, de asemenea, prin patru frecvențe diferite într-un pas de 1 MHz, cu o precizie bună a frecvenței pe întreaga durată de așteptare.

Se efectuează măsurători suplimentare pentru a studia precizia de frecvență a Link 16 FH folosind echipamente de testare mai avansate, cum ar fi Keysight E5052B și R&S FSWP. În exemplul de măsurare prezentat în tabelul 3, frecvența purtătoarei de transmisie sare la 400 MHz, 400,1 MHz, 400,2 MHz și 400,3 MHz. Intrarea de transmisie este construită pentru a produce o ieșire de 400 MHz pentru toate intervalele de salt. Durata măsurătorii este stabilită la 100 μs, ceea ce include șapte intervale complete de salt. Frecvența este măsurată la fiecare interval de timp de 128 ns. Se poate observa că PLL-ul este complet blocat la începutul timpului de așteptare. Eroarea de frecvență în timpul perioadei de așteptare depinde de performanța zgomotului de fază. Tabelul 3 prezintă performanța medie, maximă și minimă a decalajului de frecvență (diferența absolută dintre frecvența de ieșire și 400 MHz) pentru aceste șapte frame-uri consecutive de salt. În majoritatea frame-urilor, eroarea medie de frecvență este mai mică de 1 ppm. De asemenea, s-a constatat că rezultatele sunt repetabile pentru zeci de măsurători. Rețineți că măsurătorile ar putea varia în funcție de echipamente și de configurațiile de testare.

| Numărul de cadre de salt | Eroare medie de frecvență (Hz) | Eroare maximă de frecvență (Hz) | Eroare minimă de frecvență (Hz) |

| 1 | 348 | 730 | 46 |

| 2 | 424 | 997 | 4 |

| 3 | 267 | 563 | 20 |

| 4 | 327 | 892 | 7 |

| 5 | 253 | 569 | 2 |

| 6 | 394 | 903 | 12 |

| 7 | 253 | 677 | 17 |

Tabelul 3: Performanța preciziei de frecvență cu salt de frecvență Link 16

ADRV9002 oferă posibilitatea utilizatorului de a regla fin lățimea de bandă a filtrului buclei PLL. Performanța prezentată în tabelul 3 este obținută atunci când lățimea de bandă a filtrului buclei PLL este configurată la 1200 kHz. O lățime de bandă mai mare a filtrului PLL îmbunătățește timpul de resincronizare al PLL, care garantează blocarea completă a PLL înainte de începerea timpului de așteptare. Atunci când se selectează lățimea de bandă a filtrului buclei, utilizatorii trebuie să evalueze, de asemenea, performanța zgomotului de fază care se impune în aplicațiile lor.

Încărcare statică și dinamică a tabelelor cu până la 128 de intrări de frecvențe diferite

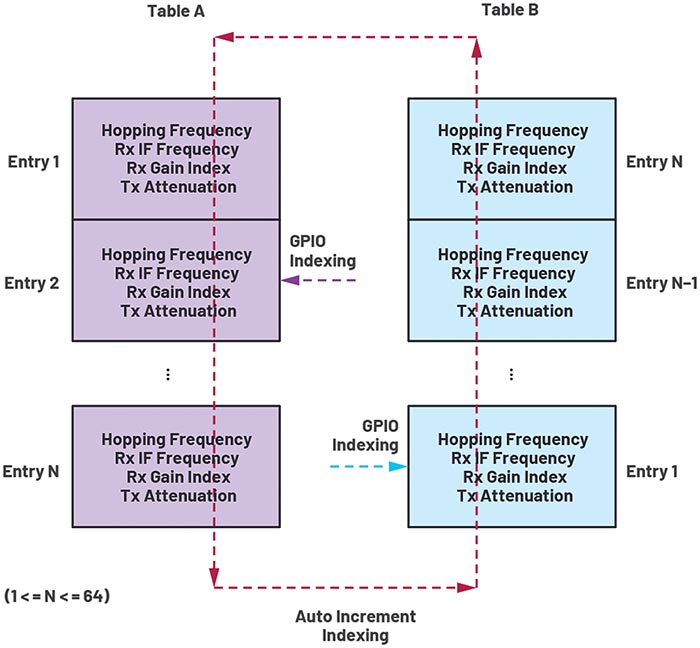

ADRV9002 utilizează un concept de tabel de salturi pentru toate modurile de FH.2) Un tabel de salturi conține o listă de frecvențe și alți parametri de funcționare pentru fiecare interval de salturi. Un tabel de salturi poate fi static, ceea ce înseamnă că este încărcat în timpul inițializării și nu este permisă schimbarea din mers. Poate fi, de asemenea, dinamic, ceea ce înseamnă că este încărcat în timpul efectuării salturilor; în acest caz, utilizatorul poate modifica conținutul tabelului din mers. Un concept similar cu cel de “ping-pong” este utilizat pentru ca utilizatorul să poată încărca opțional două tabele diferite, fiecare cu un minim de 1 până la un maxim de 64 de intrări. În timp ce un tabel este utilizat pentru frame-ul de salt curent, celălalt tabel este încărcat pentru a se pregăti pentru următorul frame de salt. Fiecare intrare notifică ADRV9002 cu privire la configurațiile pentru un anumit interval de salt. Un tabel de salturi poate fi indexat fie prin incrementarea automată a indexului (începe de la prima intrare din primul tabel până la ultima intrare din cel de-al doilea tabel și apoi se întoarce din nou la prima intrare din primul tabel cu două tabele de salturi, fie prin buclă continuă cu un tabel de salturi), fie prin accesarea unei anumite intrări în orice moment indicat prin intermediul GPIO-urilor digitale.

Figura 7 prezintă tabelele de salturi A și B, fiecare cu N intrări (1 ≤ N ≤ 64). Fiecare intrare din tabel include patru parametri cheie: frecvența de salt, frecvența intermediară (numai pentru modul IF de recepție), indicele de câștig la recepție și atenuarea la transmisie. Într-o operare TDD, utilizatorii trebuie să notifice ADRV9002 ce canal (fie de transmisie, fie de recepție) este activat pentru fiecare interval de salt, utilizând un semnal de configurare a canalului dedicat (unul pentru fiecare canal de transmisie și unul pentru fiecare canal de recepție). Prin urmare, deși fiecare intrare din tabelul de salturi conține parametri atât pentru recepție, cât și pentru transmisie, sunt utilizați numai parametrii relevanți.

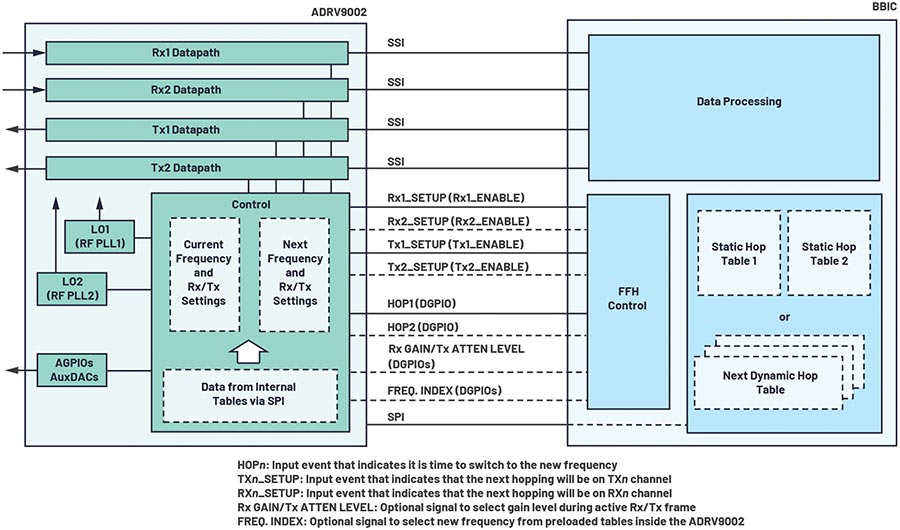

Figura 8: Schema bloc de nivel înalt a comunicației dintre ADRV9002 și BBIC în timpul saltului de frecvență. (© ADI)

Înainte de a continua discuția despre funcționarea tabelelor de salturi în FH, este util să înțelegem comunicația de nivel înalt dintre ADRV9002 și circuitul integrat BBIC (Baseband Integrated Circuit).

După cum se arată în figura 8, BBIC acționează ca element principal pentru operarea FH, care stabilește modul FH, semnalele de configurare a canalului (Rx1_ENBALE, Rx2_ENABLE, Tx1_ENABLE și Tx2_ENABLE), semnalele HOP (HOP1 și HOP2) și tabelele de salturi statice sau dinamice (frecvența de salt, frecvența IF de recepție, câștigul de recepție și atenuarea de transmisie). BBIC comunică cu ADRV9002 prin intermediul unei interfețe SPI sau DGPIOs. ADRV9002 acționează ca nod pentru FH, acceptând semnalele de la BBIC și apoi configurează calea de date și blocurile LO în consecință.

În figura 9 este descris un exemplu de încărcare dinamică a tabelelor cu o singură frecvență pentru fiecare tabel de salt A și B. Acesta este un caz extrem care permite utilizatorilor să schimbe din mers frecvența de salt în fiecare cadru. În acest exemplu este utilizat modul “PLL mux”. După cum se observă în figura 8, atât frontul ascendent, cât și cel descendent al semnalului de salt definesc limitele temporale ale unui frame de salt, fiecare constând dintr-un timp de tranziție și un timp de așteptare, după cum s-a menționat anterior. Frontul crescător al semnalului de configurare a canalului definește tipul de cadru de salt care urmărește o întârziere de un cadru (această întârziere este necesară pentru modul PLL mux).

Figura 9: Un exemplu de încărcare dinamică a tabelelor cu o frecvență per tabel folosind modul “PLL mux”. (© ADI)

Rețineți că semnalul de configurare a canalului poate reprezenta fie semnalul de configurare a transmisiei, fie semnalul de configurare a recepției. Figura 9 prezintă o versiune simplificată a semnalului. Deoarece funcționarea TDD implică atât transmisia, cât și recepția, utilizatorii trebuie să configureze separat atât semnalul de configurare a transmisiei, cât și semnalul de configurare a recepției. Pe lângă indicarea tipului de interval de salt, semnalul de configurare a canalului poate fi utilizat și pentru a declanșa încărcarea unui tabel de salturi inițiat de BBIC. Încărcarea tabelului de salturi ar trebui să fie finalizată înainte de frontul semnalului de salt după frontul de cădere al semnalului de configurare a canalului, iar apoi PLL-ul începe să se ajusteze la această frecvență la același front de salt și devine pregătit pentru următorul cadru de salt semnalat de următorul front de salt. Tabelul A și Tabelul B operează în modul “ping-pong”, astfel încât, după ce încărcarea este completă, FH operează pe frecvența unui tabel în timp ce frecvența celuilalt tabel este ajustată.

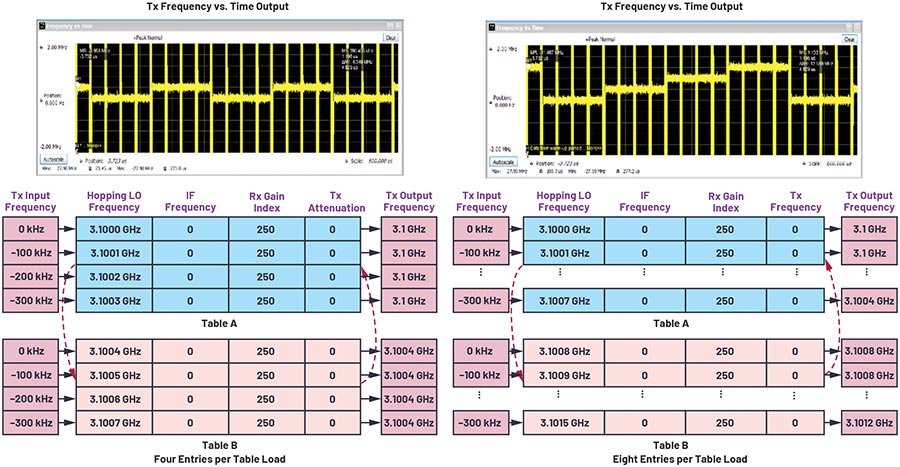

Figura 10 prezintă frecvența de transmisie în funcție de timp cu încărcarea dinamică a tabelelor pentru patru intrări per sarcină și opt intrări per sarcină. Intrarea de transmisie are patru frame-uri la frecvența de 0 kHz, -100 kHz, -200 kHz și -300 kHz și este livrată la ADRV9002 prin rularea continuă a frame-urilor (cadrelor). De asemenea, este complet aliniată și sincronizată cu cadrele de salt, astfel încât cadrul de intrare de 0 kHz se aliniază cu LO de 3,1 GHz. În timpul FH, când LO trece la următoarea frecvență, frecvența de intrare a transmisiei trece și ea la următoarea frecvență.

Tabelul A și Tabelul B sunt încărcate dinamic în timp ce se execută FH (pentru simplitate și pentru a facilita observarea, conținutul tabelului nu se schimbă de la o încărcare la alta). Pentru patru intrări per sarcină, ne așteptăm să vedem patru cadre consecutive de ieșire de transmisie la 3,1 GHz și apoi patru cadre consecutive la 3,1004 GHz, iar același model se repetă din nou și din nou. Pentru opt intrări pe sarcină, ne așteptăm să vedem patru cadre de ieșire consecutive de transmisie la 3,1 GHz, patru cadre consecutive la 3,1004 GHz, patru cadre consecutive la 3,1008 Hz și patru cadre consecutive la 3,1012 GHz, iar același model se repetă din nou și din nou. Ieșirea de transmisie prezentată în figura 8 dovedește că încărcarea dinamică a tabelelor funcționează conform așteptărilor.

Diversitatea canalelor vs. multiplexarea canalelor utilizând canale duale

După cum se observă în figura 2, ADRV9002 suportă canale duble de transmisie și recepție. FH poate fi aplicat pe ambele canale pentru a realiza fie diversitatea canalelor, fie multiplexarea canalelor.

În cazul diversității, ambele canale sar simultan prin utilizarea aceluiași PLL (unul sau două) și prin utilizarea acelorași tabele de salturi și configurații de sincronizare TDD. Capabilitatea MCS oferită de ADRV9002 ar putea fi activată pentru a asigura că mai multe canale de pe același dispozitiv ADRV9002 sau de pe dispozitive ADRV9002 diferite sunt complet sincronizate între ele cu latență deterministă. Sincronizarea de fază poate fi, de asemenea, realizată prin MCS, care este efectuată de fiecare dată când PLL-ul reajustează frecvența. Cu MCS, mai multe canale ar putea atinge sincronizarea chiar și în timpul FH, ceea ce face din ADRV9002 o soluție atractivă pentru aplicațiile de diversitate MIMO care implică FH. Descrieri mai detaliate privind cerințele și limitările utilizării MCS în timpul FH pot fi găsite în Ghidul utilizatorului pentru dezvoltarea sistemului ADRV90012).

Pentru multiplexarea canalelor, fiecare pereche de canale utilizează un circuit PLL și execută FH independent unul de celălalt. O limitare este că un FH foarte rapid, care necesită două PLL-uri pentru o pereche de canale de emisie și recepție, nu poate fi aplicat pentru multiplexarea canalelor cu un singur dispozitiv ADRV9002.

Pe lângă modul 2T2R, merită să menționăm că ADRV9002 suportă și operații 1T2R și 2T1R pentru FH, ceea ce oferă o mai mare flexibilitate pentru a satisface cerințele specifice ale utilizatorilor.

Suport pentru FH cu operare DPD

ADRV9002 suportă, de asemenea, operarea DPD atât pentru aplicații în bandă îngustă, cât și în bandă largă. Acesta corectează neliniaritatea amplificatorului de putere (PA) pentru a îmbunătăți în mod semnificativ eficiența PA, obținând în același timp performanțe conforme cu standardul raportului de scurgere a puterii pe canalul adiacent (ACPR − Adiacente Channel Power Leakage Ratio).

Figura 10: O comparație a încărcării dinamice a tabelelor cu patru intrări pe încărcare și cu opt intrări pe încărcare. (© ADI)

O caracteristică avansată a ADRV9002 este că DPD poate fi realizată împreună cu FH. În acest caz, ADRV9002 permite utilizatorilor să configureze până la opt regiuni de frecvență, iar algoritmul DPD creează o soluție optimă pentru fiecare regiune de frecvență. O soluție DPD sub forma unui set de coeficienți poate fi, de asemenea, stocată și încărcată la sfârșitul și, respectiv, la începutul unei transmisii, pentru fiecare regiune. Acest lucru asigură liniaritatea PA pentru întreaga gamă de frecvențe de salt.

Deoarece DPD este un proces de filtrare adaptivă care trebuie să capteze periodic un set de eșantioane pentru calculul coeficienților, lungimea cadrului de salt trebuie să fie suficient de mare pentru a satisface cerința privind lungimea de captare DPD. Cu toate acestea, în cazurile în care utilizatorii folosesc doar coeficienții DPD încărcați inițial, fără a fi nevoie de actualizări DPD, această restricție poate fi eliminată.

Calibrarea urmăririi ADRV9002 nu se efectuează, de obicei, în timpul unui FH rapid. Cu toate acestea, calibrările inițiale sunt efectuate pe baza mai multor regiuni de frecvență în funcție de configurațiile FH ale utilizatorilor pentru a obține cea mai bună performanță posibilă.

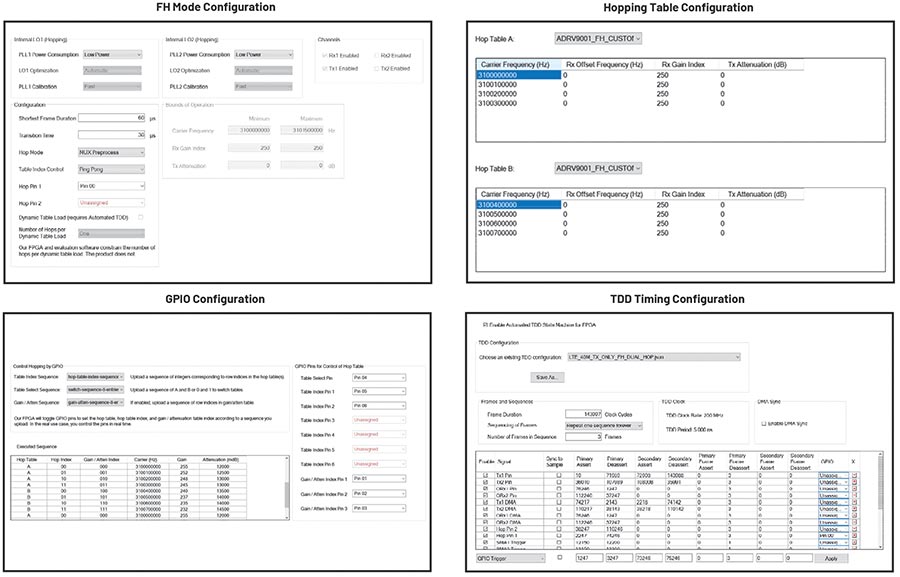

Evaluarea performanțelor FH utilizând software-ul de evaluare a transceiverului ADRV9002 (TES)

Performanța FH poate fi evaluată temeinic prin intermediul TES ADRV9002 cu ajutorul plăcii de evaluare. Atât plăcile FPGA Xilinx® ZC706, cât și ZCU102 sunt acceptate de TES.2) După cum se observă în figura 11, paginile de configurare FH sunt ușor de utilizat pentru a configura parametrii FH, inclusiv modul de funcționare FH, tabelele de salturi, setarea GPIO, sincronizarea TDD etc. Funcțiile de sincronizare FPGA sunt încorporate în TES pentru a permite utilizatorilor să controleze cu precizie sincronizarea TDD, astfel încât cadrele de transmisie sau de recepție să poată fi complet sincronizate cu cadrele de salt. Multe exemple de FH sunt, de asemenea, furnizate în TES pentru ca utilizatorii să le exploreze în continuare.

Concluzie

FH este una dintre caracteristicile avansate oferite de următoarea generație de transceivere SDR, ADRV9002. Cu două PLL-uri, mai multe moduri FH și flexibilitate în încărcarea și indexarea tabelelor de salturi, ADRV9002 oferă utilizatorilor capabilități FH deosebite pentru a face față diferitelor aplicații și pentru a îndeplini cerințele avansate ale sistemului. Toate caracteristicile pot fi evaluate în detaliu prin intermediul ADRV9002 TES și al kitului de dezvoltare software (SDK).

Referințe

1) John G. Proakis. Digital Communications, 3rd edition. McGraw-Hill, March 1994.

2) UG-1828: ADRV9001 System Development User Guide. Analog Devices, Inc., December 2020.

3) Kao Chin-Han. “Performance Analysis of a JTIDS/Link-16-Type Waveform Transmitted over Slow, Flat Nakagami Fading Channels in the Presence of Narrowband Interference.” Naval Postgraduate School, 2008.

Autor: Mizhou (Michelle) Tan,

RF Product Applications Engineer

Despre autor

Mizhou (Michelle) Tan este inginer de aplicații la Analog Devices. De aproximativ 3 ani, ea a sprijinit proiectarea și dezvoltarea de produse și aplicații de emisie-recepție RF. Înainte de a se alătura ADI, a obținut licența și masteratul în inginerie electrică la Universitatea Sichuan din China și doctoratul în inginerie electrică și informatică la New Jersey Institute of Technology în 2004. Ulterior, a lucrat ca inginer specializat în algoritmi, sisteme și software la Agere Systems, LSI Logic și Intel Corp. între 2004 și 2018. A publicat peste 15 lucrări în conferințe și reviste tehnice și deține nouă brevete eliberate în domeniul comunicațiilor fără fir și al procesării digitale a semnalelor. Poate fi contactată la mizhou.tan@analog.com.

Vizitați https://ez.analog.com

Contact România:

Email: inforomania@arroweurope.com

Mobil: +40 731 016 104

Arrow Electronics | https://www.arrow.com