Articolul trece în revistă arhitectura unui astfel de dispozitiv SoC FPGA și felul în care acesta susține proiectarea eficientă a sistemelor conectate și deterministe. Apoi, prezintă pe scurt, criteriul de referință EEMBC CoreMark-Pro privind puterea de procesare în raport cu consumul de energie, împreună cu o perspectivă asupra performanței unui SoC FPGA reprezentativ. Se analizează felul în care securitatea este integrată în aceste module și se prezintă în detaliu dispozitivele FPGA SoC de referință de la Microchip Technology, împreună cu o platformă de dezvoltare pentru accelerarea procesului de proiectare. În încheiere, este prezentată o scurtă listă a plăcilor de expansiune de la MikroElektronika, care pot fi utilizate pentru a implementa o serie de interfețe de comunicație, precum și funcții de localizare prin intermediul sistemului global de navigație prin satelit (GNSS).

Articolul trece în revistă arhitectura unui astfel de dispozitiv SoC FPGA și felul în care acesta susține proiectarea eficientă a sistemelor conectate și deterministe. Apoi, prezintă pe scurt, criteriul de referință EEMBC CoreMark-Pro privind puterea de procesare în raport cu consumul de energie, împreună cu o perspectivă asupra performanței unui SoC FPGA reprezentativ. Se analizează felul în care securitatea este integrată în aceste module și se prezintă în detaliu dispozitivele FPGA SoC de referință de la Microchip Technology, împreună cu o platformă de dezvoltare pentru accelerarea procesului de proiectare. În încheiere, este prezentată o scurtă listă a plăcilor de expansiune de la MikroElektronika, care pot fi utilizate pentru a implementa o serie de interfețe de comunicație, precum și funcții de localizare prin intermediul sistemului global de navigație prin satelit (GNSS).

FPGA-urile (Field Programmable Gate Array), subsistemele cu microcontrolere RISC-V compatibile Linux, arhitecturile avansate de memorie și interfețele de comunicații de înaltă performanță sunt instrumente importante pentru proiectanți. Acest lucru este valabil în special pentru proiectanții de sisteme conectate securizate, sisteme critice de siguranță și o gamă largă de sisteme deterministe în timp real, cum ar fi inteligența artificială (AI) și învățarea automată (ML).

Totuși, integrarea acestor elemente diverse într-un sigur sistem, conectat și determinist poate fi o activitate dificilă și consumatoare de timp, la fel ca și stabilirea interconectărilor de mare viteză pentru diferitele elemente ale sistemului. Proiectanții trebuie să includă o unitate de management a memoriei, o unitate de protecție a memoriei, capabilități de pornire (inițializare) securizată și transmițătoare de ordinul gigabiților pentru conectivitate de mare viteză. Proiectarea va avea nevoie de managementul energiei active și statice și de controlul curenților de pornire. Unele proiecte vor necesita operarea în intervalul extins de temperaturi comerciale de la 0°C la +100°C pentru temperatura de joncțiune (TJ), în timp ce sistemele din mediile industriale vor trebui să opereze cu TJ de la -40°C la +100°C.

Pentru a face față acestor provocări precum și altor probleme, proiectanții pot apela la dispozitivele FPGA SoC (system-on-chip), care combină consumul redus de putere, eficiența termică și securitatea cibernetică pentru sisteme inteligente, conectate și deterministe.

SoC-uri construite pe o structură FPGA

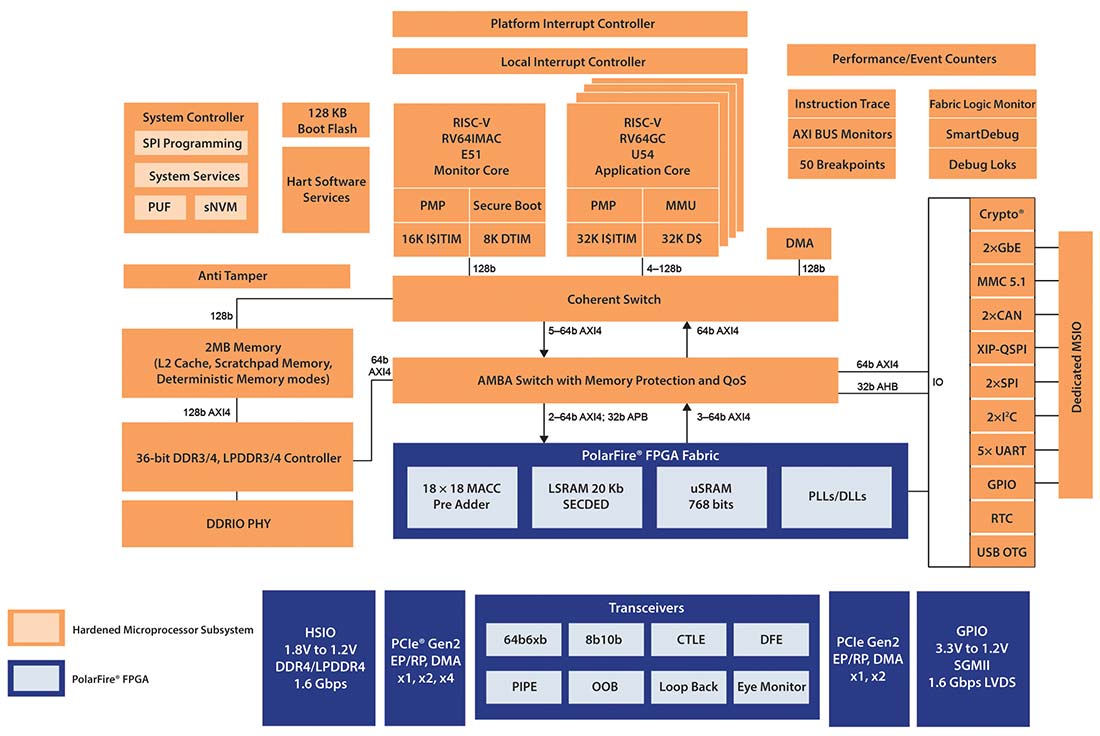

“Cipul” pentru acest SoC este o structură FPGA care conține elementele sistemului, de la FPGA la subsistemul cu microcontroler RISC-V, construit cu logică FPGA. Subsistemul cu microcontroler include un ansamblu microcontroler RISC-V cu patru nuclee, un nucleu de monitorizare RISC-V, un controler de sistem și un subsistem determinist de memorie de nivel 2 (L2). FPGA-ul din aceste SoC-uri include până la 460 K elemente logice, transmițătoare de până la 12,7 gigabiți pe secundă (Gbps) și alte blocuri de intrare/ieșire (I/O), inclusiv I/O de uz general (GPIO) și PCIe 2 (Peripheral Component Interconnect Express). Arhitectura generală a fost proiectată pentru fiabilitate. Aceasta include corecția unei erori și detectarea dublei erori (SECDED) pe toate memoriile, analiza diferențială a puterii (DPA), protecția memoriei fizice și 128 de kilobiți (Kbits) de memorie flash pentru inițializare (boot) (figura 1).

Figura 1: Toate elementele din acest SoC FPGA, inclusiv subsistemele RISC-V, sunt implementate pe structura FPGA. (© Microchip Technology).

Microchip oferă ecosistemul său Mi-V (pronunțat “my five”) de instrumente și resurse de proiectare de la terți pentru a sprijini implementarea sistemelor RISC-V. Acesta este construit pentru a accelera adoptarea arhitecturii setului de instrucțiuni RISC-V (ISA) pentru nucleele RISC-V consolidate și pentru nucleele soft RISC-V. Elementele ecosistemului Mi-V includ accesul la:

- Licențe de proprietate intelectuală (IP)

- Hardware

- Sisteme de operare și middleware

- Depanatoare, compilatoare și servicii de proiectare

Microcontrolerele RISC-V din sistemele SoC FPGA includ mai multe capabilități de depanare, cum ar fi o interfață extensibilă avansată (AXI) pasivă, configurabilă în timpul execuției și urmărirea instrucțiunilor. AXI permite proiectanților să monitorizeze datele care sunt scrise sau citite din diverse memorii și să știe când sunt scrise sau citite.

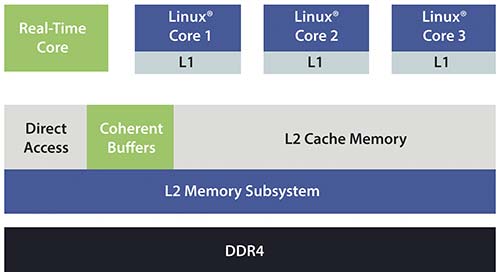

Subsistemul cu microcontroler RISC-V utilizează un pipeline în cinci etape, cu o singură instrucțiune, la fiecare ciclu de ceas. Acesta nu este vulnerabil la amenințările Spectre sau Meltdown, care pot afecta arhitecturile de tip ‘out-of-order’. Toate cele cinci microcontrolere sunt în concordanță cu subsistemul de memorie, suportând o combinație de sisteme în timp real în mod AMP (Asymmetric Multi-Processing) determinist și Linux. Caracteristicile subsistemului RISC-V includ (figura 2):

- Rularea Linux și a operațiunilor complexe în timp real

- Configurarea L1 și L2 ca memorie deterministă

- Subsistem de memorie DDR4

- Dezactivarea/activarea predicțiilor de ramificare

- Funcționarea pipeline-ului în ordine

Figura 2: Subsistemul RISC-V include mai multe elemente de procesor și de memorie. (© Microchip Technology)

Mai multă procesare cu mai puțină energie

Pe lângă avantajele pe care le oferă în ceea ce privește operarea sistemului, inclusiv suportul pentru procesare intensivă, în timp real, dispozitivele SoC FPGA sunt foarte eficiente din punct de vedere energetic. Criteriul de referință EEMBC CoreMark-PRO este un standard industrial pentru compararea eficienței și performanței microcontrolerelor în sistemele embedded. Acesta a fost special creat pentru evaluarea comparativă a performanțelor hardware și pentru a înlocui testul de referință Dhrystone.

Sarcinile de lucru CoreMark-PRO includ o diversitate de caracteristici de performanță, paralelism la nivel de instrucțiuni și utilizare a memoriei, pe baza a patru sarcini de lucru în virgulă mobilă și cinci sarcini de lucru cu numere întregi comune. Sarcinile de lucru în virgulă mobilă includ o rutină de algebră liniară derivată din LINPACK, o transformată Fourier rapidă, un algoritm de rețea neurală pentru evaluarea modelelor și o versiune îmbunătățită a criteriului de referință Livermore loops. Compresia JPEG, un analizor XML, compresia ZIP și un algoritm de hash securizat pe 256-biți (SHA-256) stau la baza sarcinilor de lucru cu numere întregi.

Modelele MPFSO95T ale acestor sisteme SoC FPGA, precum MPFS095TL-FCSG536E, pot asigura până la 6.500 Coremarks la 1,3 wați (figura 3).

Figura 3: FPGA SoC MPFS095T (linia portocalie) oferă 6 500 Coremarks la 1,3 wați. (© Microchip Technology)

Considerații privind securitatea

Aplicațiile critice din punct de vedere al siguranței precum și aplicațiile complexe în timp real destinate acestor sisteme SoC FPGA necesită o securitate puternică, pe lângă o eficiență energetică ridicată și capabilități de procesare puternice. Funcțiile de securitate de bază ale dispozitivelor SoC FPGA includ programare bitstream rezistentă la analiza diferențială a puterii (DPA), un generator de numere aleatoare reale (TRNG) și o funcție fizic neclonabilă (PUF – Physical Unclonable Function). Acestea includ, de asemenea, inițializare securizată standard și definită de utilizator, protecție a memoriei fizice, care oferă restricții de acces la memorie legate de starea mașinii, inclusiv modurile mașină, supervizor sau utilizator și imunitate la atacurile Meltdown și Spectre.

Securitatea începe cu gestionarea securizată a lanțului de aprovizionare, inclusiv cu utilizarea modulelor de securitate hardware (HSM – Hardware Security Module) în timpul testării plachetelor și încapsulării. Utilizarea unui certificat x.509 FPGA semnat digital de 768-octeți încorporat în fiecare SoC FPGA contribuie la asigurarea lanțului de aprovizionare.

Numeroase detectoare anti-manipulare pe cip sunt incluse în dispozitivele SoC FPGA pentru a asigura o funcționare sigură și fiabilă. În cazul în care se detectează o încercare de manipulare, se emite un semnal “tamper”, care permite sistemului să reacționeze în funcție de necesități. Printre detectoarele anti-manipulare disponibile se numără:

- Monitoare de tensiune

- Senzori de temperatură

- Detectoare de erori de ceas și de frecvență de ceas

- Detector activ JTAG

- Detector activ de rețea Mesh

Securitatea este asigurată și mai mult prin algoritmi AES-256 (standard avansat de criptare pe 256-biți), contramăsuri împotriva atacurilor de putere (CPA – Corelation Power Attack) cu blocuri criptate simetrice, funcții integrate de descompunere criptografică pentru a asigura integritatea datelor, PUF integrat pentru stocarea cheilor și capacități de reducere la zero a structurii FPGA și a tuturor memoriilor pe cip.

Exemple de dispozitive SoC FPGA

Microchip Technology combină aceste capabilități și tehnologii în SoC-urile FPGA PolarFire cu mai multe niveluri de viteză, temperaturi nominale și diverse dimensiuni de capsulă pentru a sprijini nevoile proiectanților pentru o gamă largă de soluții cu elemente logice între 25 K și 460 K. Sunt disponibile patru grade de temperatură (toate clasificate pentru TJ), de la 0°C la +100°C în gama comercială extinsă, de la -40°C la +100°C în gama industrială, de la -40°C la +125°C în gama auto și de la -55°C la +125°C în gama militară.

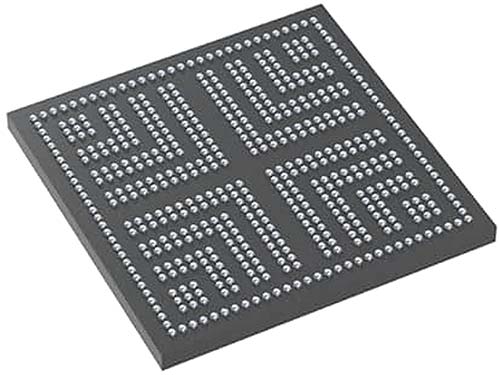

Proiectanții pot alege între dispozitive cu nivel de viteză standard sau dispozitive cu nivel de viteză -1, care sunt cu 15% mai rapide. Aceste sisteme SoC FPGA pot fi operate la 1,0 volți pentru o funcționare la cea mai mică putere sau la 1,05 volți pentru o performanță mai mare. Acestea sunt disponibile într-o gamă de dimensiuni de capsule, inclusiv 11 × 11 milimetri (mm), 16 × 16 mm și 19 × 19 mm.

Figura 4: MPFS250T-1FCSG536T2 pentru temperaturi ridicate pentru industria auto se prezintă într-o capsulă de 16 × 16 mm, cu un număr de 536 sfere și un pitch de 0,5 mm. (© Microchip Technology)

Pentru aplicațiile care au nevoie de operare la temperaturi comerciale extinse, operare la viteză standard și elemente logice de 254 K într-o capsulă de 19 × 19 mm, proiectanții pot utiliza MPFS250T-FCVG484EES. Pentru soluții mai simple, care au nevoie de elemente logice de 23 K, proiectanții pot apela la MPFS025T-FCVG484E, de asemenea cu operare la temperaturi comerciale extinse și nivel de viteză standard într-o capsulă de 19 × 19 mm. MPFS250T-1FCSG536T2 cu 254 K elemente logice este proiectat pentru sisteme auto de înaltă performanță și are o gamă de temperaturi de operare de la -40 la 125°C și un grad de viteză -1 pentru un ceas cu 15% mai rapid, într-o capsulă compactă de 16 × 16 mm cu 536 de sfere pe un pitch de 0,5 mm (figura 4).

Platformă de dezvoltare SoC FPGA

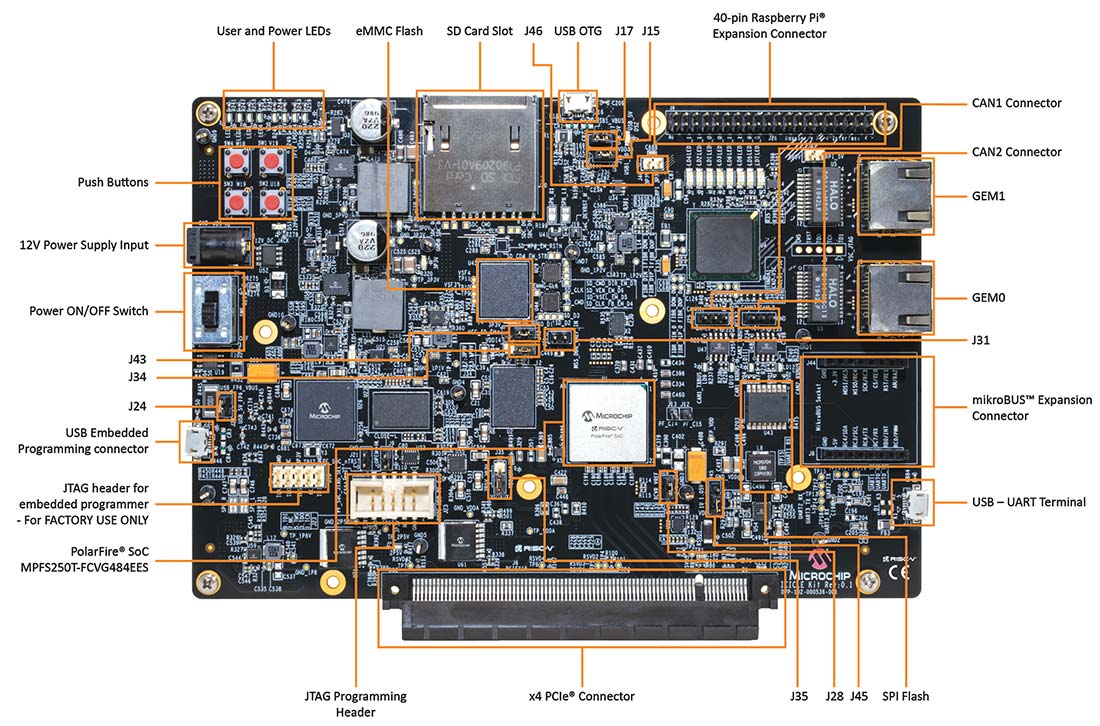

Pentru a accelera proiectarea de sisteme PolarFire SoC FPGA, Microchip oferă kitul MPFS-ICICLE-KIT-ES PolarFire SoC Icicle, care permite explorarea subsistemului microcontrolerului RISC-V cu cinci nuclee și compatibilitate Linux, cu execuție în timp real și consum redus de putere. Kitul include o licență gratuită Libero Silver, necesară pentru evaluarea proiectelor. Acesta suportă funcții de programare și de depanare într-un singur limbaj.

Figura 5: Acest mediu cuprinzător de dezvoltare SoC FPGA include conectori pentru plăci de expansiune Raspberry Pi (dreapta sus) și mikroBUS (dreapta jos). (© Microchip Technology)

Circuitele SoC FPGA sunt susținute de kitul de dezvoltare software (SDK) cu accelerator VectorBlox, care permite aplicații AI/ML cu consum redus de putere și cu factor de formă mic. Accentul este pus pe simplificarea procesului de proiectare până la punctul în care proiectanții nu trebuie să aibă experiență prealabilă de proiectare FPGA. Acceleratorul VectorBlox permite dezvoltatorilor să programeze rețele neurale eficiente din punct de vedere energetic folosind C/C++. Kitul Icicle are numeroase caracteristici pentru a oferi un mediu de dezvoltare cuprinzător, inclusiv un sistem de senzori de putere cu linii multiple pentru a monitoriza diferitele domenii de putere, un port PCIe root și memorii incluse pe placă – inclusiv LPDDR4, QSPI și eMMC Flash – pentru a rula Linux și Raspberry Pi, precum și porturi de expansiune mikroBUS pentru o serie de opțiuni de conectivitate cu și fără fir, plus extensii funcționale precum capabilități de localizare GNSS (figura 5).

Plăci de expansiune

Câteva exemple de plăci de expansiune mikroBUS includ:

MIKROE-986, pentru adăugarea de conectivitate CAN bus folosind o interfață periferică serială (SPI).

MIKROE-1582, pentru interfațarea între microcontroler și un bus RS-232.

MIKROE-989, pentru conectarea la un bus de comunicație RS422/485.

MIKROE-3144, suportă tehnologiile LTE Cat M1 și NB1, permițând conectivitate fiabilă și facilă cu dispozitivele IoT 3GPP.

MIKROE-2670, permite funcționalitate GNSS cu recepție simultană a constelațiilor GPS și Galileo plus fie BeiDou, fie GLONASS, rezultând o precizie ridicată a poziției în situații cu semnale slabe sau interferențe în cartierele urbane.

Concluzie

Proiectanții pot apela la SoC-urile FPGA atunci când dezvoltă sisteme conectate, critice din punct de vedere al siguranței și sisteme deterministe în timp real extrem de solicitante. SoC-urile FPGA oferă o gamă largă de elemente de sistem, inclusiv o structură FPGA, un subsistem cu microcontroler RISC-V cu memorii de înaltă performanță, interfețe de comunicație de mare viteză și numeroase funcții de securitate. Pentru a ajuta proiectanții să inițieze asemenea aplicații, sunt disponibile plăci și medii de dezvoltare care includ toate elementele necesare, inclusiv plăci de expansiune care pot fi utilizate pentru a implementa o gamă largă de comunicații și funcții de localizare.

Lecturi recomandate

- How to Implement Time Sensitive Networking to Ensure Deterministic Communication

- Real-Time Operating Systems (RTOS) and Their Applications

Autor: Rolf Horn – Inginer de aplicații

Autor: Rolf Horn – Inginer de aplicații

Rolf face parte din grupul European de Asistență Tehnică din 2014, având responsabilitatea principală de a răspunde la întrebările venite din partea clienților finali din EMEA referitoare la Dezvoltare și Inginerie. Înainte de Digi-Key, el a lucrat la mai mulți producători din zona semiconductorilor, cu accent pe sistemele embedded ce conțin FPGA-uri, microcontrolere și procesoare pentru aplicații industriale și auto. Rolf este licențiat în inginerie electrică și electronică la Universitatea de Științe Aplicate din Munchen, Bavaria.

Digi-Key Electronics | https://www.digikey.ro

![]()