Inovaţiile în domeniul tehnologiilor sub-micronice CMOS au permis realizarea de noi dispozitive de ceas, înalt integrate, cu instabilitate redusă, care se adresează subsistemelor de temporizare de o tot mai mare complexitate, ce pot fi identificate într-o gamă variată de echipamente, inclusiv noile generaţii de echipamente de reţele, telecomunicaţii, testare şi măsurare, precum şi transmisii video. Adesea, noile generaţii de echipamente sunt proiectate astfel încât să poată fi configurate pentru o gamă largă de aplicaţii şi standarde de comunicaţii. Un exemplu în acest sens poate fi identificat în sistemele video de producţie, în care o platformă comună trebuie reconfigurată pentru crearea unui conţinut video care să respecte standardele locale ale diferitelor ţări şi regiuni. Un alt exemplu ce poate fi dat este acela al echipamentelor de reţea multi-service, care trebuie să ofere flexibilitatea de a suporta o gamă largă de tipuri diferite de trafic de reţea, precum 10Gbps SONET/SDH, 10GbE, şi 10Gbps canal fibră.

Pentru a putea face faţă cerinţelor legate de îmbunătăţirea flexibilităţii, subsistemele de temporizare trebuie să fie adaptate la a suporta generare de semnal de ceas pe un domeniu mai mare de frecvenţe decât era anterior suficient. Subsistemele de temporizare de înaltă performanţă tradiţionale sunt construite în jurul unor bucle PLL (phase-locked loops) de frecvenţă fixă, care nu sunt uşor scalate pentru a suporta operaţii multi-frecvenţă.

Acest neajuns din punct de vedere al flexibilităţii a fost rezolvat datorită performanţelor DSP-urilor (digital signal processing) şi circuitelor de semnal mixt, oferite de noile procese tehnologice CMOS.

Anterior, subsistemele de temporizare cu instabilitate redusă erau realizate prin utilizarea multor componente discrete de mare performanţă, a unui strat de placă complex care oferea izolare la zgomot, şi o vastă experienţă PLL, care poate fi foarte dificil de găsit şi dezvoltat. PLL-urile particularizate, utilizate la construirea subsistemelor de temporizare, erau bazate pe oscilatoare cu cristal controlate în tensiune (VXCO) sau pe oscilatoare SAW controlate în tensiune (VCSO) caracterizate de înaltă performanţă, instabilitate mică şi preţ ridicat Oricum, abordarea tradiţională de implementare a subsistemelor de temporizare nu este uşor configurabilă pentru a suporta diferite frecvenţe raportate ne-întregi, datorită naturii fixe a VCXO şi VCSO. În cel mai bun caz, o arhitectură PLL bazată pe o colecţie de frecvenţe diferite VCXO sau VCSO trebuie să fie utilizată pentru a satisface operaţiile multi-frecvenţă. Problemele evidente ale acestei abordări sunt: spaţiul suplimentar necesar de placă, timpul de proiectare şi riscurile legate de aceasta operaţiune, costul şi gestionarea materialelor necesare (BOM – bill-of-materials).

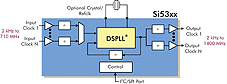

În vederea conformării la cerinţele legate de înalta performanţă, de înaltul nivel de integrare şi de operarea multi-frecvenţă, Silicon Labs’ a lansat recent familia de produse Si53xx Any-Rate Precision Clocks. Această familie de nouă dispozitive utilizează tehnologia DSPLL® a Silicon Laboratories’ pentru a oferi cel mai mare portofoliu din industrie de multiplicatoare de frecvenţă de ceas reconfigurabile de mare precizie şi atenuatoare de instabilitate.

Aceste dispozitive utilizează a treia generaţie a tehnologiei DSPLL a Silicon Labs pentru a oferi o soluţie bazată pe CI care are performanţe echivalente cu cele mai bune implementări PLL cu componente discrete care utilizează VCXO sau VCSO scumpe, oferind în acelaşi timp şi posibilitatea de reconfigurare a frecvenţei, caracteristică imposibilă proiectelor de PLL cu componente discrete. De exemplu, familia Si53xx este primul multiplicator de ceas şi atenuator de instabilitate din industrie, capabil de a genera orice frecvenţă de ieşire de la 2 kHz la 945 MHz şi de selecta frecvenţe de 1,4 GHz din orice frecvenţă de intrare între 2 kHz şi 710 MHz. Aceste posibilităţi legate de frecvenţă permit unui circuit integrat Si53xx să înlocuiască numeroase PLL-uri implementate discret sau scheme complexe de PLL-uri multi-VCXO destinate operării multi-frecvenţă. Principalele avantaje pentru client sunt costul redus, economia de spaţiu de placă, numărul de materiale necesare şi timpul de proiectare.

Familia Si53xx utilizează tehnologia DSPLL pentru integrarea tuturor componentelor discrete tradiţional utilizate în vederea implementării unui PLL într-un singur CI CMOS. Această abordare elimină toate punctele de intrare a zgomotului între fiecare element de circuit care se regăsesc în PLL-urile implementate discret, incluzând intrarea de multiplexare, VCSO, componentele buclei de filtrare, detectorul de fază, buffer-ul de ieşire etc. Ca rezultat, familia Si53xx simplifică sarcina obţinerii unor performanţe foarte bune cu privire la reducerea instabilităţii de până la 0,3 picosecunde RMS, prin oferirea unei imunităţi mult mai mari la sursele de zgomot la nivel de sistem. Pentru oferirea unei soluţii complete şi de înaltă performanţă, familia Si53xx oferă de asemenea şi o buclă de filtrare integrată cu lăţimi de bandă selectabile. Această caracteristică permite proiectanţilor să transforme lăţimea de bandă a buclei fără a schimba componente şi să optimizeze performanţele legate de instabilitate la nivel de aplicaţie.

Suplimentar, familia Si53xx suportă până la patru intrări de ceas şi cinci ieşiri de ceas diferenţiale, eliminând necesitatea unor multiplexoare externe şi buffere tradiţional utilizate în subsistemele de temporizare complexe de astăzi.

Familia Si53xx simplifică de asemenea semnificativ proiectarea şi lanţul de alimentare al arhitecturilor de temporizare moderne. Integrând complet un PLL reconfigurabil în frecvenţă în familia Si53xx, poate fi economisit timpul de proiectare asociat implementării PLL-urilor individuale, iar PLL-ul este liber să se adreseze altor elemente mai importante din proiect. În plus, Si53xx poate fi reutilizată de multe ori în cadrul unui sistem, eliminând implementarea de PLL-uri diferite şi VCXO, VCSO asociate. Acest lucru economiseşte costuri cu privire la inventar şi la problemele lanţului de alimentare asociate cu PLL-urile de înaltă performanţă implementate discret. Suplimentar, familia Si53xx utilizează tehnologie de fabricaţie de mare volum pentru CI standard, reducând astfel timpul de livrare la 4 săptămâni comparativ cu timpii mari, impredictibili, asociaţi dispozitivelor VCXO şi VCSO. Combinaţia dintre familia de circuite de ceas de precizie şi oscilatorul sau oscilatorul controlat în tensiune de la Silicon Labs creează cel mai cuprinzător portofoliu din industrie cu privire la soluţii de temporizare cu frecvenţă flexibilă şi instabilitate redusă. Soluţiile, precum cele introduse de Silicon Labs, care schimbă modelele din industrie, reprezintă cheia realizării noilor generaţii de echipamente cu o gamă largă de aplicaţii, reducând în acelaşi timp costurile, timpii de proiectare, riscurile şi problemele legate de lanţul de alimentare.

de James Wilson