Renesas dezvoltă tehnologii SoC pentru unitățile de control electronic (ECU) multidomeniu din industria auto, esențiale în era SDV

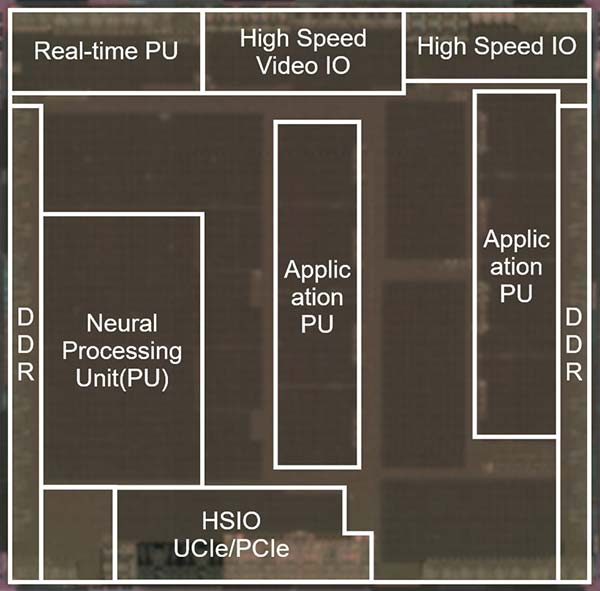

Renesas Electronics Corporation a dezvoltat trei tehnologii SoC (System-on-Chip) destinate unităților de control electronic (ECU) multidomeniu din industria auto. Acestea integrează capabilități avansate de procesare AI și arhitecturi bazate pe chipleturi, constituind o platformă tehnologică fundamentală pentru arhitecturile electrice/electronice (E/E) de nouă generație. Renesas a prezentat aceste rezultate în cadrul Conferinței Internaționale privind Circuitele în Stare Solidă 2026 (ISSCC 2026), desfășurată în perioada 15–19 februarie la San Francisco, SUA.

În era vehiculelor definite de software (SDV), SoC-urile auto necesită performanțe avansate pentru a rula simultan mai multe aplicații și trebuie să ofere scalabilitate prin chipleturi. De asemenea, acestea trebuie să îndeplinească cerințele de siguranță funcțională ale SoC-urilor auto. Pe măsură ce SoC-urile multidomeniu care deservesc calculul central devin din ce în ce mai mari și mai complexe, menținerea calității de nivel auto devine tot mai dificilă. Odată cu creșterea performanței SoC-urilor avansate, crește și consumul de energie, ceea ce face ca îmbunătățirea eficienței energetice și a siguranței să fie vitală. Pentru a răspunde acestor nevoi, Renesas a dezvoltat următoarele tehnologii noi.

Arhitectură chiplet compatibilă cu cerințele de siguranță funcțională

Pentru a îndeplini cerințele de siguranță funcțională ale SoC-urilor auto, Renesas a dezvoltat o arhitectură proprietară nouă, capabilă să susțină nivelul ASIL D chiar și într-o configurație bazată pe chipleturi. Prin combinarea interfeței standard die-to-die UCIe cu un mecanism proprietar RegionID, arhitectura previne interferențele la nivelul resurselor hardware, chiar și atunci când numeroase aplicații rulează simultan, asigurând conformitatea FFI (Freedom from Interference).

Interfețele UCIe convenționale nu dispun de capacitatea de a transmite RegionID-uri între pastilele de siliciu. Renesas a dezvoltat o metodă de mapare a RegionID-urilor în spațiul de adrese fizice, urmată de codificarea acestora în cadrul interfeței UCIe și transmiterea lor între chipleturi. Această abordare permite controlul sigur al accesului prin unitatea de gestionare a memoriei (MMU) și prin nucleele în timp real, îndeplinind cerințele de siguranță funcțională specifice arhitecturilor chiplet.

În plus, prin menținerea lățimii de bandă între procesoare și magistrala de memorie, interfața UCIe a demonstrat în teste o rată de transfer de până la 51,2 GB/s, apropiată de limita superioară a comunicațiilor intra-SoC. Această tehnologie oferă atât scalabilitate, cât și un nivel ridicat de siguranță pentru SoC-urile auto de înaltă performanță.

Capacități avansate de procesare AI și calitate de nivel auto

Calitatea la nivel auto este esențială pentru sistemele SDV. Renesas a dezvoltat un SoC pe tehnologie de 3 nm care îmbunătățește performanța unităților de procesare neurală (NPU) dedicate sarcinilor AI, menținând în același timp standardele stricte de calitate impuse în domeniul auto. În ultimii ani, NPU-urile au crescut semnificativ în dimensiune, suprafața acestora fiind cu aproximativ 1,5 ori mai mare comparativ cu generațiile anterioare. Această evoluție a condus la creșterea latenței semnalului de ceas între sursele partajate și circuitele individuale.

Pentru a rezolva această problemă, Renesas a reproiectat arhitectura distribuției ceasului prin segmentarea generatoarelor de impulsuri de ceas (CPG), care în proiectele anterioare funcționau la nivel de modul și introducerea mini-CPG-urilor (mCPG) la nivel de submodul. Această abordare reduce semnificativ latența ceasului și permite respectarea cerințelor stricte de sincronizare.

Totuși, utilizarea mCPG-urilor multistrat adaugă complexitate în sincronizarea ceasului de testare, esențială pentru atingerea obiectivului de zero defecte în aplicațiile auto. Renesas a integrat circuite dedicate de testare în arhitectura ierarhică CPG și a unificat traseul semnalului pentru ceasurile de funcționare și cele de test. Noul model permite sincronizarea mCPG-urilor de nivel superior și inferior sub o singură sursă de ceas în modul de testare, facilitând ajustarea unificată a fazei.

Ca rezultat, Renesas a obținut un nivel de calitate aliniat cerințelor de zero defecte, chiar și pentru SoC-uri de mari dimensiuni, asigurând fiabilitatea ridicată necesară SoC-urilor auto SDV de nouă generație.

Control și monitorizare avansate ale puterii pentru eficiență energetică și siguranță îmbunătățite

Pentru a atinge nivelul ridicat de performanță necesar SoC-urilor auto, menținând în același timp eficiența energetică și siguranța, Renesas a dezvoltat o tehnologie avansată de control al puterii, bazată pe mai mult de 90 de domenii de alimentare. Aceasta permite reglarea precisă a consumului, de la câțiva miliwați până la câteva zeci de wați, în funcție de condițiile de operare.

În plus, Renesas a împărțit switch-urile de putere (PSW) în structuri inelare și structuri în serie, pentru a reduce căderile IR (căderile de tensiune) asociate cu creșterea densității curentului în tehnologiile de procesare avansate. La pornirea alimentării, PSW-ul inelar limitează curenții de vârf, iar PSW-ul în serie contribuie la uniformizarea impedanței în cadrul domeniului de alimentare. Împreună, aceste soluții reduc căderile IR cu aproximativ 13% comparativ cu proiectele convenționale.

Pentru a îndeplini cerințele de siguranță funcțională ASIL D, arhitectura dual core lockstep (DCLS) controlează nucleele master și checker prin switch-uri și controlere de alimentare independente. În acest mod, chiar dacă apare o defecțiune într-unul dintre circuite, aceasta poate fi detectată prin mecanismul lockstep. În plus, fiecare semnal de poartă al PSW-ului este monitorizat printr-un mecanism de tip loopback, permițând detectarea stărilor OFF în cazul unei defecțiuni.

Monitorizarea tensiunii este realizată cu ajutorul unui voltmetru digital (DVMON – Digital Voltage Meter), proiectat pentru rezistență ridicată la variațiile de temperatură. Această abordare îmbunătățește toleranța la îmbătrânire cu aproximativ 1,4 mV.

Aceste tehnologii permit dezvoltarea unor SoC-uri auto de înaltă performanță, care oferă atât eficiență energetică, cât și siguranță funcțională.

Noile tehnologii sunt implementate în SoC-ul R-Car X5H de la Renesas, destinat ECU-urilor auto multidomeniu. Cu R-Car X5H, producătorii pot accelera evoluția vehiculelor definite de software (SDV), garantând siguranța și susținând aplicații precum conducerea autonomă și habitaclul digital.

Renesas Electronics Corporation