Procesoarele şi FPGA-urile (field-programmable gate arrays) merg adesea mână în mână la proiectarea unui sistem. Acest lucru oferă inginerului flexibilitate atât în ceea ce priveşte software-ul cât şi hardware-ul. În 2002, Xilinx a adus împreună cele două dispozitive prin lansarea familiei sale Virtex II Pro.

de Tony Storey, Application Engineer, Digi-Key

Continuare din numărul trecut.

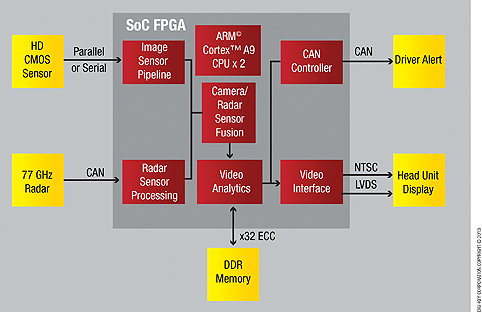

Ca şi în cazul nucleelor “de pe raft”, natura programabilă a FPGA furnizează proiectantului o oportunitate excelentă de a construi procesoare particulare. Arhitecturile Cyclone SoC şi Zynq au fost dezvoltate specific cu această utilizare în minte – dispozitivele din ambele familii au magistrale de I/O largi pentru transferul datelor între secţiunile de logică programabilă şi procesor.

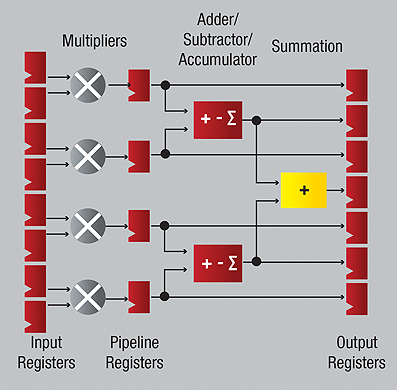

De-a lungul anilor, furnizorii de FPGA-uri au adăugat suport pentru calcul de mare viteză, în special pentru aplicaţii de procesare semnal. Multiplicatorii pot consuma o mulţime de spaţiu într-o arhitectură standard bazată pe elemente de tip tabelă de căutare. Cea mai eficientă cale de a implementa multiplicarea în celulele programabile este de a utiliza aritmetică bit-serială. Multiplicatorii sunt lenţi deoarece lucrează prin adăugarea şi translatarea a câte unui bit la un moment dat. Multiplicatorii de tip bit-serial excelează atunci când sunt utilizaţi în matrice paralele masive, putând suporta viteze mari de transfer de date. Natura simplă şi compactă a multiplicatorului bit-serial face posibilă utilizarea multora într-un singur FPGA. Dacă întârzierea nu este importantă, ele reprezintă încă o bună alegere.

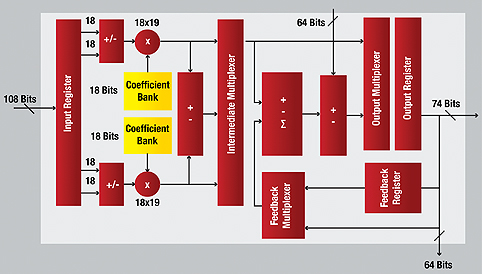

Pentru o procesare mai rapidă, distribuitorii de FPGA-uri adaugă un lanţ de transport logic pentru a permite proiectanţilor să implementeze sisteme suplimentare mai rapide de transport-anticipat şi transport-salvare în logica programabilă. Numeroase arhitecturi FPGA, inclusiv produse optimizate ca şi cost precum Altera Cyclone şi Xilinx Spartan-6, includ acum blocuri multiplicatoare multiplicatoare pentru utilizare în aplicaţii DSP de mare viteză.

Aceste blocuri pot fi chiar înguste pentru a reduce consumul de spaţiu, dar pot fi legate cu uşurinţă între ele pentru a forma multiplicatoare mai complexe pe 32 şi 64 de biţi. Celulele logice programabile pot adăuga suport pentru caracteristici mai complexe precum aritmetică în virgulă mobilă. Unele arhitecturi oferă o varietate de nuclee DSP potrivite aplicaţiilor ţintă. Aceste nuclee conţin unităţi înguste de 9 biţi potrivite pentru semnale audio şi de comunicaţie şi nuclee mai largi pentru procesare de imagine şi video.

Mulţumită naturii programabile a materialului FPGA, este posibilă construirea de coprocesoare adaptate necesităţilor sistemului. Reconfigurarea parţială poate permite diferitelor blocuri de coprocesoare să fie încărcate, executate şi apoi înlocuite cu un alt algoritm. De exemplu, într-un algoritm de procesare audio, materialul FPGA poate realiza procesare spectrală utilizând transformata Fourier rapidă (FFT) urmată de o filtrare utilizând un filtru cu răspuns la impuls finit (FIR) încărcat în aceeaşi secţiune odată ce analiza spectrală a fost finalizată.

Programabilitatea FPGA ajută de asemenea la simplificarea trecerii datelor printr-un element coprocesor. În cazul unui FFT, implementarea algoritmului într-un procesor de uz general este adesea lentă deoarece modelul de acces date “fluture” necesită implicarea de preluări şi scrieri repetate de valori temporare în memoria cache sau cea principală – întârzierea cauzată de aceste accese poate însemna că unităţile aritmetice logice interne sunt lipsă de date. FPGA-ul face posibilă inserarea acestor valori temporare într-o structură complexă ce asigură că elementele DSP dispun mereu de date relevante.

Materialul FPGA oferă avantaje pentru operaţii care nu se potrivesc într-un ALU standard. De exemplu, funcţiile criptografice şi mulţi algoritmi utilizaţi în comunicaţie digitală, precum decodoarele Viterbi şi Turbo, utilizează adesea modulo şi alte aritmetici non-standard. Cu un control complet asupra elementelor logice, un ALU particularizat bazat pe FGPA va depăși aproape întotdeauna o emulare software care se execută pe un nucleu de procesor standard.

Apariţia unor limbaje precum OpenCL este probabil să uşureze construirea de elemente de coprocesoare care pot fi prevăzute şi îndepărtate dacă este necesar. Deşi OpenCL a fost dezvoltat original pentru a face puterea de calcul a unităţilor de procesare grafică (GPU) disponibilă pentru programatorii mult mai obişnuiţi să lucreze cu arhitecturi de uz general precum ARM sau x86, companii precum Altera au îmbrăţişat OpenCL ca o cale de a face mai uşoară construirea de motoare de calcul particularizate.

Funcţiile OpenCL iau forma unor nuclee de calcul – bucle vectoriale strânse utilizate pentru a procesa în paralel elemente multiple de date. OpenCL conţine un mediu de rulare ce încarcă nucleele de calcul şi datele respective în procesoarele ţintă, pornind executarea şi apoi preluarea rezultatelor.

Unealta de compilare are grijă de convertirea algoritmului exprimat în limbajul OpenCL într-o implementare potrivită pentru configurarea cu un FPGA.

O altă cale de a descărca software de la procesor într-un FPGA este de a reduce frecvenţa întreruperilor. Fiecare întrerupere comandă procesorului să se oprească indiferent ce face pentru a captura şi trimite un fragment de date printr-un port de intrare/ieşire, fiecare întrerupere implică împingerea conţinutului unui registru în stivă ocupând cicluri de procesor.

Motorul de calcul analogic (ACE) în Microsemi SmartFusion este un mic procesor paralel independent care controlează diferitele porturi analogice de I/O suportate de dispozitiv. (vezi diagrama din numărul trecut)

ACE combină un motor de secvenţiere eşantioane (SSE – sample sequencing engine) cu un motor de post procesare (PPE – post-processing engine). SSE capturează datele de la intrările analogice, le trece către PPE care poate executa funcţii precum filtrare trece jos pentru a îndepărta zgomotul, şi transformă datele într-un format convenabil pentru procesor. Transferul acestor funcţii în hardware asigură că pot fi utilizate pentru a reduce foarte mult întreruperile pe procesor.

Tehnici similare pot fi natural implementate în FPGA-uri ce dispun de aceste caracteristici pentru a reduce problema întreruperilor pentru alte nuclee de procesoare. Cu un FPGA există întotdeauna mai multe căi de a aduce împreună procesarea software şi viteza de operare hardware paralelă.

Digi-Key Corporation

www.digikey.com