Pentru ca aplicația să funcționeze corect, trebuie să fie stocate operații logice, intervale de tensiune sau niveluri logice și trebuie transferate semnale între circuite integrate digitale. Cea mai simplă soluție este utilizarea modulelor logice. Aceasta asigură transferul unui circuit digital simulat către aplicație.

Fiecare familie logică are caracteristicile sale specifice. Modulele diferă în ceea ce privește nivelul și tensiunea de alimentare, raportul semnal/zgomot, timpul de propagare prin poartă, frecvența maximă, consumul de energie, precum și ‘fan-in’ și ‘fan-out’.

Două familii conduc piața

Figura 1: Simbolul standard pentru porți logice cu o gamă largă de variante în ceea ce privește capsula și numărul de terminale. (Sursa imagine: Rutronik)

Piața este dominată de două familii majore – fiecare cu diverse subfamilii. În primul rând, poarta logică TTL (logică bazată pe tranzistori bipolari) și, în al doilea rând, modulele bazate pe tehnologia CMOS (Complementary Metal Oxide Semiconductor), adică tranzistoare cu efect de câmp cu polaritate opusă.

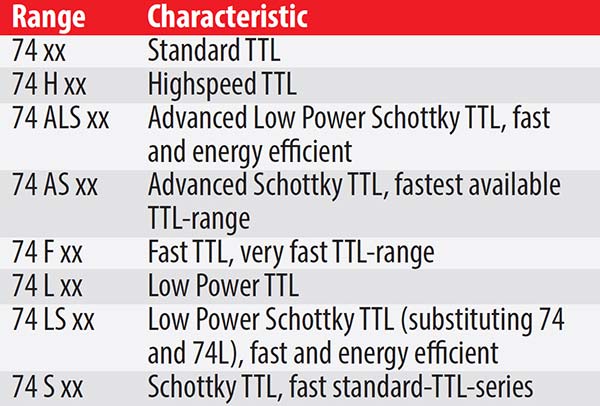

Membrii familiei TTL constau dintr-un set de porți logice construite din tranzistoare, diode și rezistențe. Acestea acoperă, practic, toate aplicațiile imaginabile cu circuite cu nivel de integrare scăzut și mediu. Cuplarea intrării și ieșirii semnalului se face prin intermediul tranzistoarelor. Porțile TTL se caracterizează prin timpi de comutare scurți și un curent de ieșire relativ ridicat, ceea ce permite controlul direct al unor sarcini mai mici. Posibilitatea driverului de a avea un curent de ieșire ridicat este însoțită în același timp de un consum ridicat de curent de liniște și, prin urmare, și de un necesar de putere relativ ridicat. Aceasta, la rândul său, obligă la suprafețe mari de cip pentru a disipa pierderile de căldură rezultate și limitează densitatea de integrare. Exemple de familii TTL sunt enumerate în tabelul 1.

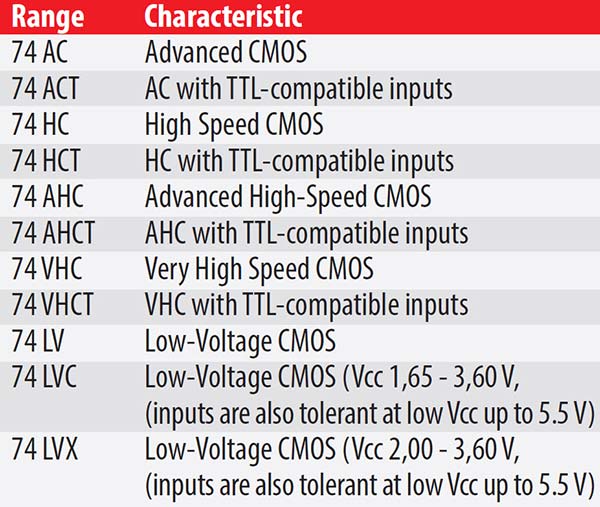

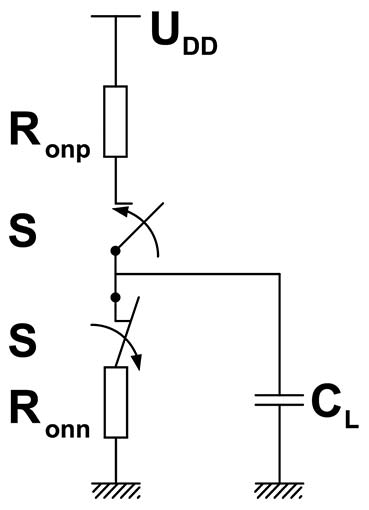

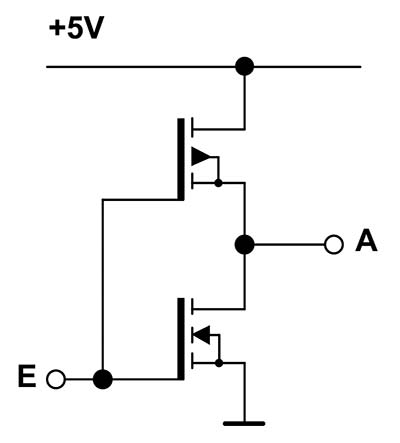

Circuitele logice bazate pe tehnologia CMOS sunt în prezent cele mai utilizate, datorită diverselor avantaje pe care le oferă, cum ar fi un consum mai mic de putere și mai puțin zgomot. Acestea se bazează pe combinarea unui MOSFET canal N cu un MOSFET canal P complementar (Figura 2).

În fiecare stare de comutare, unul dintre cele două MOSFET-uri este blocat, iar curentul de liniște este aproximativ zero; circulă doar curenți de scurgere de izolație și de joncțiune, de câțiva nanoamperi. Mai mult, circuitul este în mare parte lipsit de rezistențe parazite, ceea ce înseamnă că porțile CMOS nu consumă putere în regim static. Cu toate acestea, consumul mediu de curent al porții CMOS depinde de frecvența de comutare și crește odată cu aceasta: Consumul predominant apare în timpul încărcării și descărcării capacităților tranzistorului CT. La încărcare, energia este stocată și, în același timp, aceeași cantitate este transformată în căldură în FET-ul de încărcare. La descărcare, energia stocată în capacitor este transformată în căldură în FET-ul de descărcare. Într-un ciclu scăzut-înalt-scăzut, energia este astfel transformată în căldură. Acest lucru duce la următoarea pierdere de energie:

Figura 2: Modulul de bază al tuturor porților CMOS este un etaj format din două MOSFET-uri complementare. Aceasta reprezintă cea mai simplă formă a unui invertor. (Sursa imagine: Rutronik)

PV = W/t = W · f = CT · V2DD · f

Exemple de familii CMOS sunt enumerate în tabelul 2.

Niveluri cu tehnologie TTL și CMOS

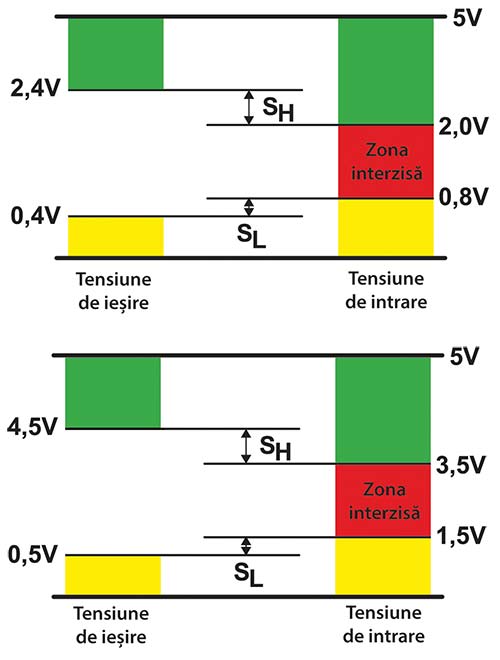

Într-o poartă logică, gamele de tensiune pentru controlul semnalelor de ieșire sunt mai înguste decât cele pentru semnalele de intrare. Atunci când mai multe circuite de bază sunt interconectate, semnalele de interferență și zgomotul nu provoacă un comportament eronat al circuitului global, în anumite limite. Zonele care nu se suprapun între intrare și ieșire (sau nivelurile înalte (High) și joase (Low)) sunt denumite raporturi semnal/zgomot SH și SL.

O intrare TTL detectează un 0 logic între 0 și 0,8V și un 1 logic între 2 și 5V pe întreaga gamă de tensiune de alimentare. Intervalul de tensiune între 0,8 și 2V este o zonă interzisă. Un semnal aplicat în acest domeniu pentru o perioadă lungă de timp poate provoca oscilația porții și declanșa o funcționare defectuoasă. La ieșire, nivelurile pentru 1 sunt cuprinse între 2,4 și 5V, iar nivelurile pentru 0 sunt cuprinse între 0 și 0,4V (Figura 4, stânga).

Cu o tensiune de alimentare de 5V, o poartă CMOS detectează un nivel logic 0 cuprins între 0V și 1,5V la intrare și un nivel logic 1 cuprins între 3,5 și 5V. La ieșire, valorile sunt, în consecință, de la 0 la 0,5V pentru 0 logic și de la 4,5 la 5V pentru 1 logic.

Dacă se aplică o tensiune de 5V, rapoartele semnal/zgomot pentru CMOS sunt deja mai mari decât pentru TTL (Figura 4). Deoarece nivelurile depind de tensiunea de operare pentru CMOS – se aplică următoarea regulă de bază: Uih= 0,7-Uv – apare posibilitatea de a crește raportul semnal/zgomot la intrarea porții folosind o tensiune de operare mai mare. Această opțiune nu există pentru TTL.

Un avantaj clar al tehnologiei CMOS: cu cât este mai mare raportul semnal/zgomot al unei porți, cu atât este mai mică probabilitatea de funcționare defectuoasă și cu atât mai zgomotos poate fi un semnal fără a declanșa defecțiuni.

Combinarea diferitelor familii logice

Atunci când se procesează, se conectează și se condiționează semnale, procesul de combinare a porților, chiar și din familii diferite (de exemplu, TTL și CMOS), devine inevitabil. Trebuie să se țină seama de diverse proprietăți, cum ar fi nivelul și fan-out-ul.

O comparație între diagramele de nivel TTL și CMOS (Figura 4) arată clar că o intrare TTL poate fi conectată direct la o ieșire CMOS, deoarece tensiunile de ieșire ale CMOS se află în intervalul nivelurilor de intrare TTL. Cu toate acestea, trebuie să se asigure că modulul CMOS livrează un curent suficient pentru a controla circuitele TTL. Totuși, acest lucru nu se aplică și invers, deoarece nivelul TTL-1 se află în intervalul interzis pentru CMOS. Această problemă poate fi rezolvată cu un CMOS din seria 74HCT care este compatibil cu TTL în ceea ce privește pinii și funcția. De asemenea, aceasta face ca rezistența pull-up, altfel necesară, să fie redundantă.

Fan-out-ul specifică sarcina de încărcare a unei ieșiri, adică numărul maxim de intrări care pot fi controlate de o ieșire a porții fără a depăși limitele nivelurilor de tensiune necesare pentru un 0 sau 1 logic. Se calculează ca fiind raportul dintre curentul maxim de ieșire și curentul maxim de intrare al porților care sunt controlate:

Figura 4: Nivelul TTL (sus) cu SH sau SL = 0,4 V în comparație cu nivelul CMOS cu SH sau SL = 1V la 5V (jos). (Sursa imagine: Rutronik)

Fan-out = IO,max / II,max

În cazul porților TTL, tensiunea de intrare redusă limitează fan-out-ul maxim atunci când se distribuie curentul. O valoare tipică este de 20 de porți.

În cazul CMOS, capacitatea circuitelor integrate controlate acționează ca un factor limitativ, deoarece curentul de intrare DC al circuitelor integrate logice CMOS este de ordinul microampermetrilor. Capacitatea de intrare în acest caz este de aproximativ 10pF. Suma capacităților care pot fi conectate la o ieșire este de până la 500pF. Teoretic, 50 de circuite integrate logice CMOS pot fi conectate la o singură ieșire. Cu toate acestea, trebuie remarcat că frontul crescător al formei de undă a semnalului se aplatizează, crescând astfel întârzierea de propagare. În consecință, timpii de comutare devin mai lungi. Așadar, trebuie efectuată în prealabil o evaluare funcțională a configurației plăcii pentru a se asigura că porțile logice CMOS funcționează corect. Cu toate acestea, creșterea numărului de intrări duce la o creștere a consumului de energie, ceea ce, la rândul său, mărește pierderea de putere.

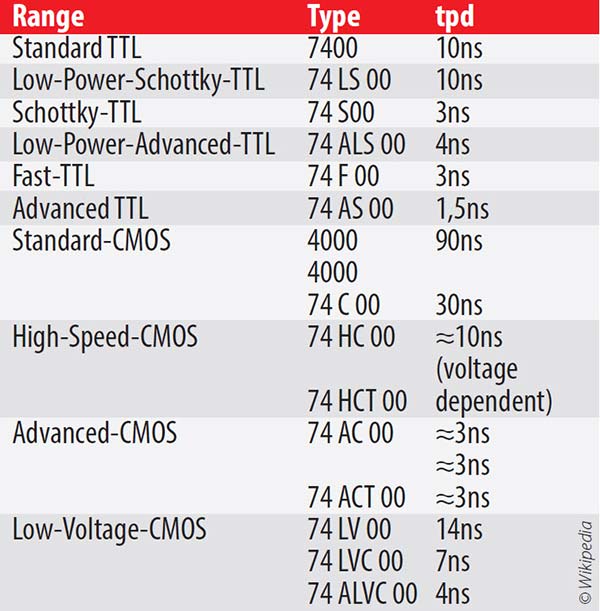

Timpul de comutare a porții tpd (propagation delay – întârziere de propagare), adică întârzierea tipică pe care o suferă un semnal între intrarea și ieșirea porții, trebuie, de asemenea, luată în considerare atunci când se combină diferite porți. La TTL, cauza întârzierii este timpul de comutare al tranzistorului. În cazul componentelor CMOS, timpul necesar pentru încărcarea sau descărcarea capacității de sarcină provoacă întârzierea de propagare (comutarea FET-ului). Tabelul 3 prezintă o comparație a timpilor de comutare a porților componentelor TTL și CMOS.

Există o mulțime de familii

O gamă largă de opt familii logice este oferită numai de Diodes. Cu sediul în Plano, Diodes este un producător american de dispozitive electronice semiconductoare, cum ar fi diode, redresoare, tranzistoare și MOSFET-uri. Compania are un portofoliu larg de componente de înaltă performanță și cu amprentă mică, disponibile prin intermediul Rutronik.

Familiile logice de la Diodes cuprind circuite logice cu o singură poartă (AHC, AHCT, LVC și AUP), cu două porți (LVC și AUP) și circuite logice standard (HC, HCT, AHC, AHCT, LV și LVC) pentru aplicații industriale, de comunicații, electronice de consum și informatice. Versiunile compatibile cu industria auto (cu sufixul Q) sunt calificate conform AEC-Q100, produse în fabrici certificate IATF-16949 și supuse procedurilor PPAP.

Familiile logice de la Diodes cuprind circuite logice cu o singură poartă (AHC, AHCT, LVC și AUP), cu două porți (LVC și AUP) și circuite logice standard (HC, HCT, AHC, AHCT, LV și LVC) pentru aplicații industriale, de comunicații, electronice de consum și informatice. Versiunile compatibile cu industria auto (cu sufixul Q) sunt calificate conform AEC-Q100, produse în fabrici certificate IATF-16949 și supuse procedurilor PPAP.

O caracteristică specială a portofoliului Diodes este familia de circuite logice AUP cu consum de putere foarte redus. Membrii acesteia au histerezis mic la intrare, ceea ce îi face mai puțin susceptibili la problemele cauzate de semnalele care cresc sau scad lent. Familia AUP este disponibilă în șapte variante de capsule și este deosebit de potrivită pentru aplicațiile portabile alimentate de la baterie, cum ar fi telefoanele mobile, tabletele, cititoarele electronice, jocurile, camerele foto, notebook-urile și dispozitivele IoT.

Produsele logice de uz general cu o singură poartă sau cu două porți sunt disponibile în variante de capsule mici, cum ar fi SOT25/26/353/363. Acestea reprezintă alegerea perfectă pentru aplicații standard, de exemplu, 74AHC și 74AHCT cu o gamă a tensiunii de alimentare de la 2,0 la 5,5V și, respectiv, de la 4,5 la 5,5V. Curenții mai mici de declanșare asigură o mai mare rezistență a circuitelor la interferențe în caz de întreruperi. Versiunea 74AHCT este, de asemenea, compatibilă cu intrări TTL.

Familia 74LVCx permite aplicații de tensiune cu semnal mixt, deoarece intrările sale pot fi controlate între 3,3V și 5,5V și pot fi utilizate direct cu niveluri de tensiune de intrare TTL.

Caracteristici ale CMOS și TTL

Deoarece tehnologia CMOS are o cerință de curent redusă, sursa de alimentare este mai ieftină și mai ușor de proiectat pentru gestionarea alimentării decât în cazul TTL.

• Componentele CMOS nu consumă putere în regim static, dar consumul de energie crește odată cu ciclul de ceas. În schimb, componentele TTL oferă un consum de putere constant.

• Datorită timpilor mai lungi de creștere și descreștere în porțile CMOS, semnalele digitale necesită o procesare mai puțin complexă.

• Familiile CMOS au o gamă mai largă de tensiuni de operare decât TTL. Aceasta variază de la 3V la 15V. Prin urmare, CMOS poate fi integrat atât în circuite TTL, cât și în circuite analogice care operează cu tensiuni mai mari. Astfel, nu este necesar un regulator de tensiune, ceea ce reduce pierderile de energie și costurile componentelor.

• TTL demonstrează o rezistență mai mare la interferențele electromagnetice. Modulele CMOS, pe de altă parte, sunt relativ sensibile la încărcarea statică și trebuie să fie protejate împotriva descărcărilor electrostatice (ESD).

• Bilanțul energetic al componentelor poate fi dedus din viteza înmulțită cu puterea per poartă (SPP – Speed Power Product). Acesta este dat în picojouli per poartă. Cu cât valoarea lor este mai mică, cu atât mai bine. CMOS depășește considerabil TTL cu o valoare de la 0,18 pJ/poartă la 150 pJ/poartă.

• În ceea ce privește circuitul de intrare, există o diferență fundamentală între cele două tehnologii: Intrările TTL nefolosite pot fi lăsate libere dacă mediul este lipsit de interferențe, deoarece acestea au întotdeauna nivelul 1. În cazul CMOS, fiecare intrare de poartă trebuie conectată la un potențial definit, deoarece acestea pot capta cu ușurință pulsuri de interferență, ceea ce duce la stări de circuit nedefinite.

• CMOS are un raport semnal/zgomot mai mare între nivelurile de semnal scăzut și ridicat decât TTL și, prin urmare, este mai puțin susceptibil la interferențe.

Autor:

Thomas Bolz, Corporate Product Manager Standard Products, Rutronik

Rutronik | https://www.rutronik.com

![]()