O privire în interiorul generației următoare de dispozitive SoC – QorIQ LS

O arhitectură de tip software-aware (software conștient) este o platformă care permite clienților să exploateze pe deplin și ușor capabilități arhitecturale și caracteristici prin biblioteci cu performanțe optimizate și prin software ușor de pus în aplicare. Arhitectura Layerscape combină performanța extremă a celor mai capabile procesoare de comunicații de astăzi, cu modelele de programare de nivel înalt, familiare şi modulare, care sunt utilizate în întreaga lume.

Charles Babbage, inventator din secolul al 18-lea, a avut dreptate. Deși “maşina diferențială” de cinci tone, primul computer mecanic făcut de el, a avut mai mult de 20.000 de piese în mișcare, aceasta a fost remarcabilă datorită faptului că era reprogramabilă. Pentru tot acel hardware, exista partea software care a făcut-o extraordinară. Studii recente în care au fost implicate echipe de ingineri din întreaga lume arată că, de obicei, timpul alocat pentru scrierea software-ului este mult mai mare decât cel pentru crearea de hardware. Companiile de inginerie, de asemenea, angajează mai mulți programatori decât ingineri, iar majoritatea covârșitoare a dezvoltatorilor alege mediul lor software înainte de a selecta un cip-ul sau cip-urile MPU pe care vor rula programul. Colegii lor din marketing știu că software-ul oferă calea cea mai directă către diferenţierea produsului. Codul original asigură “valoarea adăugată”: diferențiatorul care stabilește că un produs este deosebit într-o piață aglomerată și în mișcare continuă. Acest lucru nu înseamnă că partea hardware nu este crucială: dimpotrivă chiar. Sfântul Graal al proiectării hardware este de a face partea hardware în sine, transparentă. Ea trebuie să atragă atenţia rapid, să aibă un nivel ridicat de performanță optimizată, și un software conștient.

Pașii următori

În cazul în care un MPU este doar un mijloc pentru un scop final – o poartă de acces sau o cheie pentru a debloca o bază de software stabilită – atunci este important să fie selectată cheia potrivită. O arhitectură de procesor populară, cum ar fi Intel® x86, aduce cu ea o rezervă enormă de software x86, cea mai mare parte fiind dezvoltată pentru piața de calculatoare personale. De asemenea, arhitecturi de tip Power Architecture®, ARM® sau MIPS vin cu o calitate de membru implicit al “cluburilor” software respective. Dacă intenția este de a rula software de PC, un procesor x86 este alegerea obligatorie. Pentru piețele de produse integrate sau industriale, opțiunile unui dezvoltator sunt mult mai flexibile.

Inițial, atunci când cele mai multe programe erau scrise în limbaj de asamblare, alegerea procesorului determina alegerea programatorilor. Dezvoltatori specializați în diferite instrucțiuni CPU setează şi fixează în mod activ ISA-urile lor preferate.

Codul în sine nu a fost mai transportabil decât talentul; software-ul scris pentru o familie de procesoare era inutil pentru o altă familie, exceptând, poate ca un exemplu al modului în care poate fi structurat codul data următoare. Pasionații de codificare ar susţine că un software scris în limbaj de asamblare este eficient și rapid, în timp ce managerii lor de afaceri l-au ridiculizat, de obicei, pentru capacitatea lentă de dezvoltare, pentru că este prea greu de depanat, fiind specific doar unei singure platforme hardware, pentru că este dificil de portat și de nepătruns pentru cineva care nu este implicat în efortul de dezvoltare original.

În mod ideal, software-ul trebuie să fie simultan rapid și eficient în execuție, și rapid și ușor în dezvoltare și mentenanță. Nicio tehnologie nu a atins vreodată acest ideal, deși o trecere de la programarea la nivel de asamblare la limbaje de nivel superior, cum ar fi C, a ajutat considerabil. În prezent, mai puțin de 10% din dezvoltatorii de produse integrate folosesc un limbaj de asamblare pe scară largă; mai mult de 70% folosesc C sau C++ aproape exclusiv. Sistemele de operare portabile au ajutat, de asemenea. Linux®, în special, este disponibil pentru aproape orice arhitectură de procesor și orice configurație hardware, ceea ce face platforma aproape universală pentru dezvoltatorii embedded.

Între limbajele de programare portabile și platformele omniprezente, industria este mai aproape ca oricând de atingerea echilibrului ideal de eficiență a codului (în termeni de performanță de execuție) și dezvoltare eficientă (în termeni de cost, de timp pentru lansarea pe piață și mentenanță). Echilibrul de performanță privind flexibilitatea și ușurința în utilizare au devenit ca o cursă spațială în care sunt angrenați furnizorii de procesoare integrate. Acolo este locul în care ideea de arhitectură “software-aware” devine crucială. O arhitectură de software-conștient este o platformă care permite clienților să exploateze pe deplin și ușor capacități arhitecturale și dispune de biblioteci optimizate performante, precum și de un software ușor de pus în aplicare.

Introducere în arhitectura Layerscape

Arhitectura Layerscape este arhitectura sistemului de bază a ultimei generații a seriei de dispozitive SoC – QorIQ LS. Proiectat de la început pentru a profita de noile realități de dezvoltare, abstractizare și eficiență (în ambele sensuri ale cuvântului), arhitectura Layerscape a fost creată pentru a “expune” fiecare performanță a cip-ului într-un mod pe care programatorii să-l găsească foarte accesibil. Arhitectura extinde tendința actuală spre proiectarea de cip-uri multi-nucleu (atât omogene, cât și eterogene) pentru a obține performanță maximă, în timp ce se abstractizează complexitatea hardware pentru a face dezvoltarea software eficientă, mentenabilă, clară, rapidă și relativ simplă. Pe scurt, arhitectura Layerscape echilibrează performanța și eficiența unui cod scris de mână în limbaj de asamblare, cu ușurința de utilizare a limbajelor de nivel înalt și mentenanța de cod modernă. Arhitectura Layerscape poate fi privită ca o evoluție a variantei “Data Path Acceleration Architecture” (DPAA) găsită în seriile QorIQ P și T – o infrastructură de susținere a partajării interfețelor de rețea și a acceleratoarelor de nuclee multiple CPU și acceleratoarelor însăși.

Arhitectura Layerscape extinde arhitectura DPAA, în care straturile separate ale modelului de rețea ISO sunt accelerate separat și în mod corespunzător, depinzând de un cip specific. Unele cip-uri pot manipula compresia (de exemplu) în software, în timp ce altele au acceleratoare hardware dedicate. Astfel, funcția este transparentă pentru programatori şi simplifică trecerea implementării de la un cip la altul, fără a modifica niciun cod. Interfețele cu programare structurată conțin compresia (în acest exemplu), astfel că nici codul care o apelează sau care este apelat de aceasta nu trebuie să știe modul de compresie implementat efectiv. Aici, din nou, abstractizarea păstrează eficiența și performanța, precum și bunul simț al dezvoltatorilor.

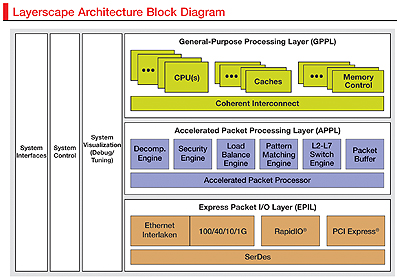

În seria QorIQ LS, fiecare procesor de comunicații este organizat logic în trei straturi, așa cum se arată în figura 1. Stratul de procesare de scop general (GPPL), stratul de prelucrare de pachet accelerat (APPL) și stratul de intrare/ieșire pachet expres (EPIL), reprezintă aproximativ straturile superior, mediu și inferior ale modelului ISO standard. Este irelevant faptul dacă cipul este (sau nu) partiționat fizic în acest mod; programatorul percepe lucrul acesta, indiferent de modul în care ar putea fi echipat un cip individual. La cel mai scăzut nivel, stratul I/O packet expres (figura 1, în maro), furnizează performanța de viteză între toate interfețele de rețea care sprijină capabilități de comutare L2+ și conține interfețele cipului pentru datagrame de rețea precum Ethernet, Interlaken, Serial RapidIO®, HiGig și PCI Express®. Interfețe importante precum USB sau SATA, dar care nu au legătură cu cele menţionate mai sus, nu fac parte din acest strat de interfață, dar pot exista în blocul “interfață de sistem” al cipului, așa cum se vede în stânga diagramei din figura 1. Deși, strict vorbind, interfața PCI Express nu este o interfață de rețea, utilizarea sa frecventă între cardurile dintr-un rack motivează includerea ei în acest strat.

Stratul de mijloc (figura 1, evidențiat în albastru) conține în cip elemente de prelucrare de pachete ce pot fi acceleratoare cablate, motoare programabile sau o combinație a celor două. APPL oferă capabilități autonome și valoare adăugată definite de client, printr-o secvențialitate tradițională, sincronă, ce rulează la finalizarea modelului și este complet programabil prin intermediul unui limbaj integrat, C bazat pe programare structurată. Din nou, aceste elemente vor fi în contact cu procesoarele de uz general prin intermediul unor interfețe bine definite care conțin detaliile lor (cât și al procesoarelor) implementate în așa fel încât păstrează valoarea codului dezvoltatorului.

Procesoarele de uz general (figura 1, evidențiat în verde) sunt, în mod clar, de uz general și se oferă, gratuit pentru utilizatori / dezvoltatori pentru a le folosi la sistemul (sistemele) lor de operare, la aplicații, la cod de nivel înalt și la alte caracteristici cu valoare adăugată. În conformitate cu valorile de abstractizare ale arhitecturii Layerscape, eficiența și independența hardware, acest strat poate sprijini atât Power Architecture, cât și nuclee ARM.

De notat este faptul că tehnologia Power Architecture folosește, în general, ordonarea “big-endian byte”, în timp ce tehnologia ARM este în mod normal “little-endian”. Arhitectura Layerscape, însă sprijină fericit ambele tehnologii. În mod clar, arhitectura hardware modulară se pretează la multe configurații de cip diferite și este o arhitectură unică, cu software consistent pe platformă. Cadrul hardware modular și flexibil include straturi independente, scalabile pentru a maximiza performanța și eficiența puterii în portofoliul QorIQ. După cum s-a menționat mai sus, aceste configurații pot include chiar procesoare de uz general, din familii de seturi de instrucțiuni diferite, acordând astfel dezvoltatorului o pârghie spre baze de cod diferite. Modularitatea arhitecturii Layerscape permite, de asemenea, performanță crescută sau mai scăzută, uneori în același soclu fizic de circuit integrat, păstrând, în același timp, codul client.

O implementare fundamentală pe cip, de pildă, ar putea include numai interfețele de nivel scăzut (Ethernet, de exemplu), iar la nivelul cel mai de sus un procesor de uz general (de exemplu, ARM sau nuclee Power Architecture), fără acceleratoare intermediare între ele. În acest caz, stratul EPIL ar efectua analiza pe pachet (packet parsing), clasificare și distribuție pentru a încadra șirurile (nereprezentate). Un procesor de uz general (sau, poate, mai multe procesoare) ar consuma atunci acele pachete de la șiruri. Extinzând acest concept pe mai multe porturi Ethernet, același cip ar putea acționa ca un strat 2, comutator, profitând de avantajul arhitecturii Layerscape, prin caracteristica sa inclusă, “link de agregare” (link aggregation). Un cip mai generos echipat ar putea include hardware în stratul mijloc (APPL) pentru o clasificare de pachete cu granulație fină, IPsec, SSL, LRO/TSO și alte sarcini avansate de tip offloads inline. În mod similar, stratul de nivel scăzut EPIL ar putea identifica anumite tipuri de pachete, pe care să le redirecționeze direct la acceleratoare relevante din stratul de mijloc APPL, ocolind în întregime procesoarele de uz general.

Piatra de temelie a soluției este software-ul care permite programatorului să valorifice rapid și ușor puterea arhitecturii. Soluția începe cu biblioteci de rețea optimizate pentru funcții accelerate hardware, cum ar fi IPSec, deep packet inspection, redirecționarea IP, NAT/FW etc., care să permită dezvoltatorului de sisteme încorporate să se concentreze pe software cu valoare adăugată, și nu pe adaptare de performanță. Bine definitele DataPath și interfețele de control API sunt standarde pentru multe aplicații de rețea și sunt ușor de extins pentru aplicații personalizate, folosind un model de programare C imperativ. În plus, un cadru software furnizând servicii standard, cum ar fi depanare și profilare, managementul resurselor, virtualizare și inițializare, sunt furnizate pentru a asigura ușurința de utilizare. În cele din urmă, implementări de referință pentru aplicații-cheie cum ar fi software definit de rețea, wireless transport/backhaul, terminare TCP și rutare, vor fi furnizate nu numai pentru a reduce investițiile dumneavoastră în R&D, dar și pentru accelerarea timpului de lansare pe piață.

Rezumat

Arhitectura Layerscape combină performanța extremă a celor mai capabile procesoare de comunicații de astăzi, cu modelele familiare, modulare, cu nivel înalt de programare, folosite la nivel mondial. Ea face accesibile motoare de comunicații avansate, fără a necesita o atestare avansată în ingineria hardware. Mai important, nu se cere reînvățarea detaliilor fiecărei implementări de cip, așa că o generație de dispozitive din seria QorIQ LS face loc succesoarei sale. Modelul de programare bine definit și delimitat supraviețuiește de la cip la cip, generație de generație, bazându-se pe activitatea dezvoltatorilor, fiind astfel mai folositor, în loc să renunțe la el pe măsură ce se modifică implementarea hardware. Pe scurt, arhitectura Layerscape păstrează cel mai important și cel mai valoros aspect al oricărei echipe de dezvoltare: software-ul său de diferențiere. Încă o dată, hardware-ul corect se dovedește a fi cheia pentru deblocarea software-ului potrivit.

Pentru mai multe informații, accesaţi link-ul: freescale.com/QorIQ

Freescale Semiconductor România S.R.L.

București

Tel: 021 3052 400

officero@freescale.com

www.freescale.ro