Interfața periferică serială (SPI) este de foarte mulți ani una dintre cele mai utilizate metode de conectare a dispozitivelor periferice externe, cum ar fi senzorii și memoriile, la un microcontroler gazdă. Simplitatea unei interfețe seriale cu sincronizare prin semnal de ceas pentru a extinde funcția unui microcontroler a făcut ca interfața SPI să fie întâlnită în multe proiecte de-a lungul anilor care au urmat, fiind implementată în aproape toate tipurile de microcontrolere.

Interfața periferică serială (SPI) este de foarte mulți ani una dintre cele mai utilizate metode de conectare a dispozitivelor periferice externe, cum ar fi senzorii și memoriile, la un microcontroler gazdă. Simplitatea unei interfețe seriale cu sincronizare prin semnal de ceas pentru a extinde funcția unui microcontroler a făcut ca interfața SPI să fie întâlnită în multe proiecte de-a lungul anilor care au urmat, fiind implementată în aproape toate tipurile de microcontrolere.

SPI a apărut pentru prima dată în anii 1980, pe microcontrolerele dezvoltate de companiile Motorola și National Semiconductor Corporation, prin care ofereau o modalitate simplă de extindere a funcțiilor disponibile pe microcontrolerele pe 8-biți din acea vreme. Astfel, a devenit rapid disponibilă o gamă largă de dispozitive periferice, de exemplu memorii EEPROM, convertoare analogice/digitale și dispozitive de extensie I/O. Dispozitivele periferice SPI au devenit extrem de populare, deoarece foloseau doar câțiva pini ai procesorului gazdă, iar utilizatorii nu pierdeau un port I/O complet, așa cum se întâmpla în cazul perifericelor care erau conectate la microcontrolerul gazdă prin intermediul unui bus paralel. De asemenea, acest lucru a însemnat o reducere a consumului de energie în comparație cu dispozitivele paralele, precum și apariția unor capsule mai mici și mai compacte, ceea ce le făcea mai rentabile. Dimensiunile reduse, atât ale capsulei, cât și ale implementării magistralei, au permis ca acestea să ocupe mai puțin spațiu pe plăcuța de circuit imprimat.

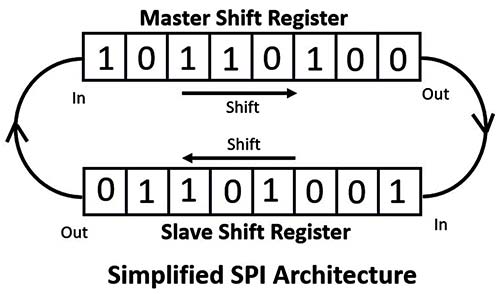

În prezent, SPI a devenit aproape un standard de facto pentru mulți utilizatori care doresc să conecteze dispozitive periferice la microcontrolerele lor. La început, standardul se bucura de o mare popularitate în rândul celor care doreau să adauge mici memorii nevolatile sistemului lor, dar, treptat, numărul dispozitivelor care acceptă SPI a crescut, ajungând să ofere o mare diversitate de funcții. Interfața SPI utilizează un protocol serial sincron simplu, care poate fi considerat un buffer serial amplu, partajat între două dispozitive, un master și un slave. Acest lucru permite sincronizarea datelor între două dispozitive sub controlul unui semnal de ceas generat de dispozitivul principal (master).

Interfața SPI este controlată de dispozitivul master, care se poate conecta la unul sau mai multe dispozitive slave folosind patru semnale logice. De regulă, acestea sunt cunoscute sub numele de:

SCLK: Serial Clock (semnal de ceas generat de către master)

MOSI: Master Out Slave In (transmiterea datelor de la master la slave)

MISO: Master In Slave Out (transmiterea datelor de la slave la master)

CS: Chip Select (semnal activ de nivel scăzut (Low) generat de master pentru a adresa dispozitivele individuale și a iniția transferul de date între acestea).

La familia de microcontrolere RA, SCLK este uneori cunoscut și sub numele de RSPCK, iar semnalul CS este cunoscut sub numele de semnal de selectare a dispozitivului slave (SSL).

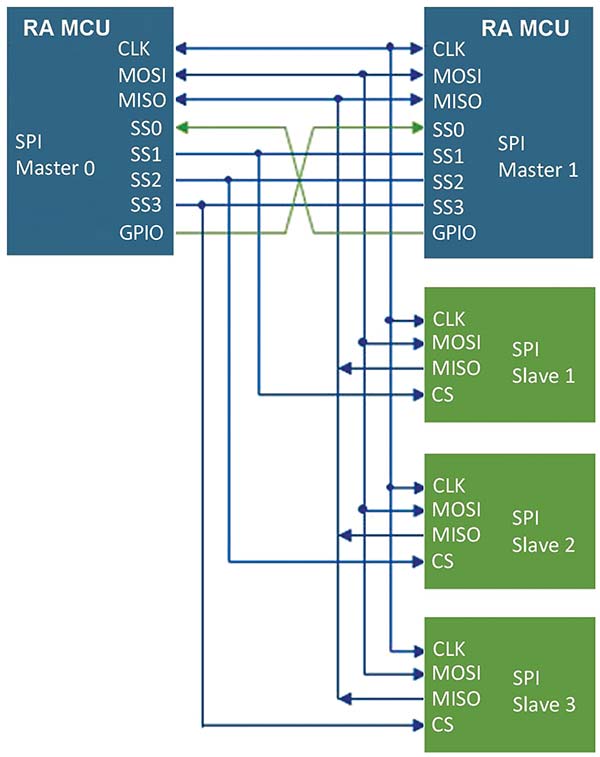

În timp ce SPI poate utiliza o mulțime de pini pentru bus, este în măsură să opereze la viteze mari, unele dispozitive suportând tranferuri de date la frecvențe de până la 60 MHz sau mai mult. SPI are mai multe avantaje, printre care se numără acceptarea de comunicații full duplex, viteză mare și un mecanism de comunicații simplu, care necesită un driver software simplu și ușor de dezvoltat. Figura următoare ilustrează schema bloc a unei aplicații SPI tipice, cu mulți pini de intrare/ieșire utilizați pentru a susține transferul serial de date, în special dacă aplicația are mai multe periferice.

SPI este un excelent exemplu de protocol non-standard. Diferitele implementări dezvoltate cu mulți ani în urmă de diverși furnizori de semiconductori au dus la convenții variate de denumire pentru aceste semnale logice, în funcție de dispozitiv și de producător. Pentru a complica și mai mult lucrurile, diferiții furnizori au dezvoltat dispozitive periferice SPI care pot comunica în diverse “arome” de SPI care pot complica configurarea comunicațiilor între mai multe dispozitive.

Diversele dispozitive slave pot fi proiectate să comunice prin deplasarea datelor în timpul frontului crescător sau descrescător al ceasului, fie imediat ce CS devine valid, fie în ciclul următor. Acest lucru este cunoscut sub numele de “polaritatea ceasului”, iar datele sunt eșantionate pe frontul descrescător sau crescător corespunzător, cunoscut sub numele de “faza ceasului”.

Dispozitivele slave pot exista în oricare dintre aceste variante, astfel încât masterul nostru SPI trebuie, de asemenea, să fie capabil să comunice în toate variantele posibile pentru a putea dialoga cu fiecare dispozitiv slave SPI potențial. În plus, dispozitivele slave SPI pot să transfere datele fie LSB, fie MSB mai întâi, cu o lungime de date selectabilă. Prin utilizarea mai multor pini ca Chip Selects, este posibilă conectarea la un master a mai multor dispozitive periferice diferite și selectarea fiecăruia în parte pentru a inițializa comunicațiile.

Utilizarea unui master SPI pe un microcontroler pentru a-l interfața cu mai multe periferice SPI, toate cu cerințe de comunicare diferite, poate deveni destul de complexă. Acest lucru poate crește foarte mult dimensiunea driverului software necesar pentru interfața SPI, iar necesitatea de a suporta diferitele “arome” de comunicație poate necesita, de asemenea, reconfigurarea interfeței SPI între fiecare transfer de date efectuat către un dispozitiv slave diferit.

Interfața SPI de pe familia RA este un periferic destul de complex, deoarece trebuie să facă față unei game largi și diferite de metode de comunicare acoperite de SPI. Interfața SPI poate fi programată prin alegerea polarității ceasului sau a fazei ceasului, o lungime de transfer de date programabilă, selectabilă între 8 și 32 de biți, o viteză de transfer programabilă și posibilitatea de a controla direct diverse sincronizări SPI, cum ar fi întârzierea înainte de eliberarea semnalului “Chip Select” și întârzierea până la următorul acces. Sunt acceptate ambele tipuri de comunicații, full și half duplex, atât pentru operațiunile de tip “doar transmisie”, cât și pentru cele de tip “doar recepție”.

Interfața SPI de pe familia RA poate controla automat până la 4 semnale “Chip Select”, permițând manipularea automată a până la 4 dispozitive. Dispozitivele suplimentare pot fi gestionate cu suport software folosind pinii standard de I/O. Interfața SPI de pe RA implementează, de asemenea, o funcție selectabilă de inversare a pinilor.

Totodată, interfața SPI de pe RA dispune de buffere pentru transmisie și recepție pe 128-biți, care permit utilizarea a până la 4 cadre de date transferabile într-o singură rundă de transmisie sau recepție. Aceste cadre de date sunt selectabile de către utilizator între 1 și 4 pentru fiecare transfer.

Interfața SPI poate detecta o mare varietate de erori, putând astfel genera o întrerupere. De asemenea, pot fi generate întreruperi în cazul în care bufferul de recepție este plin sau bufferul de transmisie este gol sau când transmisia este completă. Aceste evenimente pot fi, de asemenea, utilizate pentru a declanșa un DTC (Data Transfer Controller) sau un transfer DMA.

În sfârșit, interfața SPI poate funcționa în modul master sau poate fi utilizată în modul slave cu un dispozitiv master extern.

Un transfer SPI este declanșat de scrierea datelor în registrul de date SPI. Acest registru poate fi accesat la nivelul unui octet, cuvânt sau cuvânt lung, iar interfața SPI va transfera automat datele în memoria tampon de transmisie și va începe transferul serial.

În cazul în care utilizatorii doresc să comunice cu mai multe dispozitive, utilizând diferite variante de SPI cu viteze de transmisie diferite, aceștia vor trebui să configureze interfața SPI de fiecare dată și să declanșeze transferul. Acest lucru poate ocupa o mare parte din timpul de lucru al unității centrale de procesare, așa că ar fi mult mai ușor dacă am găsi o modalitate de a realiza automat configurarea și transmiterea datelor.

Interfața RSPI implementată pe familia RA utilizează un secvențiator de comenzi avansat în logica SPI pentru a permite configurarea unei serii de transferuri automate între diferite dispozitive slave SPI și pentru a reconfigura interfața între fiecare transfer. Acest lucru poate reduce foarte mult cerințele pentru rutina de tratare a întreruperilor SPI, deoarece utilizatorii nu mai trebuie să reconfigureze interfața SPI între fiecare transfer către un dispozitiv diferit și, de asemenea, poate accelera timpii de transfer din același motiv. Utilizarea secvențiatorului de comenzi pentru a gestiona interfața SPI poate, de asemenea, să economisească putere în cadrul aplicației, deoarece procesorul poate fi inactivat în timp ce secvențiatorul de comenzi automatizează colectarea de date de la diferite dispozitive. Acesta poate utiliza fie controlerul DMA pe cip, fie DTC pentru a prelua date din SRAM pe cip pentru a fi trimise sau pentru a încărca datele primite în memoriile tampon din SRAM pentru a fi analizate ulterior.

Secvențiatorul de comenzi SPI permite executarea unei secvențe de până la 8 transferuri într-o secvență în buclă. După ce secvența este finalizată, aceasta va începe din nou cu prima comandă, așa cum se arată în secvențele disponibile de mai jos.

Lungimea secvenței este 1 (n = 0→0→…)

Lungimea secvenței este 2 (n = 0→1→0→…)

Lungimea secvenței este 3 (n = 0→1→2→0→…)

Lungimea secvenței este 4 (n = 0→1→2→3→0→…)

Lungimea secvenței este 5 (n = 0→1→2→3→4→0→…)

Lungimea secvenței este 6 (n = 0→1→2→3→4→5→0→…)

Lungimea secvenței este 7 (n = 0→1→2→3→4→5→6→0→…)

Lungimea secvenței este 8 (n = 0→1→2→3→4→5→6→7→0→…)

Pentru fiecare comandă, pot fi setate o serie de funcții, inclusiv rata de biți, polaritatea și faza ceasului, nivelul logic de selectare a dispozitivului slave, lungimea transferului de date și bitul cel mai semnificativ (MSB) sau bitul cel mai puțin semnificativ (LSB). Pentru fiecare comandă, utilizatorii pot, de asemenea, să selecteze ce pin “Chip Select” să folosească pentru fiecare comandă, selectând astfel un anumit dispozitiv slave. Aceștia pot seta timpul după finalizarea transferului în care semnalul Chip Select este eliberat și pot seta întârzierea de acces după transfer înainte de începerea transferului următor.

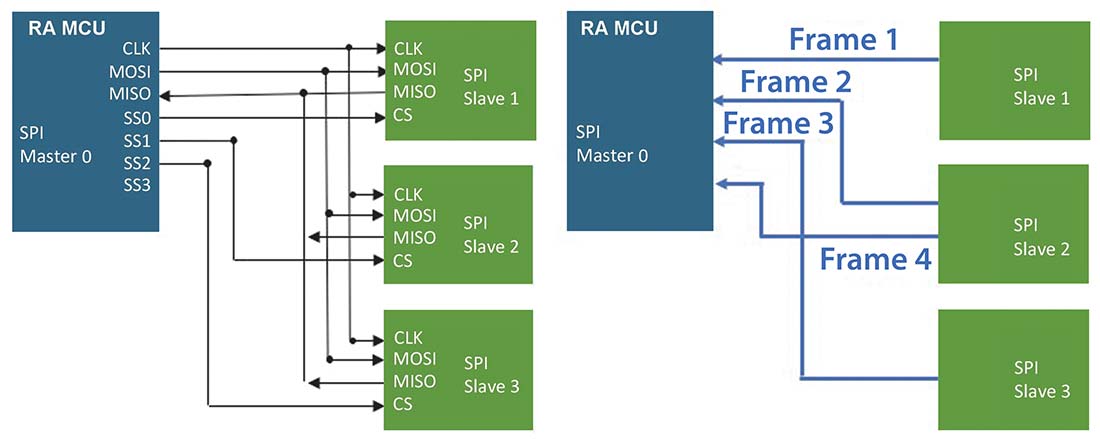

Figura de mai jos prezintă un exemplu de sistem care utilizează SPI pentru a conecta microcontrolerul RA master la 3 dispozitive slave. Ne putem imagina un astfel de sistem în care RA colectează periodic date de la mai multe dispozitive senzoriale, cum ar fi senzori de presiune, umiditate sau temperatură. Secvențiatorul de comenzi ne permite să gestionăm colectarea automată a datelor de la acești senzori, cu o sarcină redusă din partea unității centrale de procesare.

Exemplu de sistem: operare SPI multi-slave utilizând un microcontroler RA MCU – (Stânga) și Fluxul de date în cadrul sistemului – (Dreapta)

Secvențiatorul de comenzi este utilizat pentru a gestiona comunicațiile dintre aceste dispozitive. În exemplu, folosim o lungime a secvenței de 4, deoarece lungimea secvenței este independentă de numărul de accesări ale fiecărui dispozitiv slave. În această secvență, accesăm dispozitivul slave 2 de două ori, efectiv la o rată dublă față de celelalte două dispozitive slave. Fiecare transfer de date între master și slave are proprii parametri, stabiliți ca parte a structurii comenzii.

Utilizarea secvențiatorului de comenzi reduce semnificativ sarcina CPU pentru a gestiona citirea dispozitivelor seriale care utilizează interfața SPI. Atunci când este combinat cu DTC sau cu controlerul DMA pentru a automatiza transferul de date, se obține un instrument puternic de gestionare a datelor provenite de la dispozitive externe, cum ar fi senzori și memorii, complet automat și cu o intervenție minimă din partea CPU. Aceasta este o modalitate excelentă de a colecta date de la un număr de dispozitive senzoriale diferite fără implicarea CPU, iar atunci când este combinată cu unele dintre celelalte caracteristici care se găsesc, de obicei, pe un microcontroler RA, cum ar fi controlerul DMA, poate automatiza complet citirea și stocarea de date de la senzori externi, fără nicio sarcină suplimentară a unității centrale.

Interfața SPI a continuat să evolueze și să își extindă capabilitățile, cele mai recente versiuni oferind posibilitatea de a suporta viteze mai mari de transfer de date, optimizate în special pentru a susține o gamă largă de dispozitive de memorie externă, cum ar fi PSRAM și dispozitive Flash.

Printre acestea se numără Quad SPI, unde interfața SPI a fost îmbunătățită pentru a suporta transferul de date pe un bus paralel pe 4-biți, permițând un transfer de date mai rapid către și de la memorii externe. Unele periferice QSPI sunt compatibile cu funcționalitatea XiP (execute in place), care permite microcontrolerelor să descarce și să ruleze codul din aceste memorii “seriale” externe, ca și cum codul ar fi stocat în memoria locală a microcontrolerului. Unele dintre cele mai recente dispozitive merg un pas mai departe, astfel încât perifericul permite utilizatorului să cripteze codul înainte ca acesta să fie stocat în memoria externă. Perifericul SPI este capabil să decripteze acest lucru “din mers” (on the fly) și să permită microcontrolerului să execute aplicația decriptată rezultată, menținând astfel securitatea aplicației.

Cele mai recente dezvoltări au dus la apariția unor periferice care suportă OctaSPI și HexaSPI, unde sunt disponibile 8, respectiv 16 linii de date pentru a permite transferuri de date de mare viteză de la memoriile externe.

Interfața SPI a debutat prin a susține dezvoltarea microcontrolerelor simple pe 8-biți, dar acum poate suporta cele mai noi dispozitive de înaltă performanță pentru aplicații IoT avansate. Acest lucru depășește cu mult ceea ce a fost prevăzut inițial, atunci când au fost dezvoltate primele interfețe SPI.

Pentru a afla mai multe despre implementarea interfeței SPI în microcontrolerele RA și despre secvențiatorul de comenzi SPI, precum și despre unele dintre cele mai recente implementări SPI în oricare dintre microcontrolerele RA de la Renesas, vizitați pagina web www.renesas.com/RA.

![]() Autor:

Autor:

Graeme Clark,

Inginer principal

Renesas Electronics Europe | https://www.renesas.com

![]()