Sisteme de mică putere

Staţiile de comunicaţii fără fir (wireless) şi echipamentul de acces/ acumulare reprezintă aplicaţii de infrastructură în care gestionarea puterii şi căldurii reprezintă parametri critici. Staţiile fixe lucrează în condiţii de mediu extreme, iar DSLAM, mini-DSLAM, digital loop carriers (DLC) precum şi echipamentele de acces înrudite trebuie să fie păstrate reci pentru o bună funcţionare.

Creatorii de sisteme adoptă noi strategii de gestionare a puterii în aceste tipuri de aplicaţii. Una dintre metode este realizarea unor sisteme mai mari fizic, conform specificaţiilor Advanced Telecom Computing Architecture (ATCA), sisteme ce pot disipa mai multă căldură. ATCA a fost acceptată fără rezerve de producătorii de echipamente şi furnizorii de componente, ca o platformă de referinţă. Existenţa unui factor comun printre furnizorii de echipamente reduce semnificativ timpul şi costul de prototipare.

Gradul în care ATCA va prelua producţia de sisteme este încă necunoscut. Puterea, spaţiul şi costul sunt consideraţii majore, în special în cazul echipamentelor de mare volum. Unii furnizori sunt îngrijoraţi şi de pierderea proprietaţilor de know-how şi a afacerii sigure de upgrade.

O abordare alternativă adoptată de proiectanţi este aceea de maximizare a numărului de canale pe mW. Utilizarea inteligentă a caracteristicilor şi tehnologiei noilor procesoare, permite un factor de formă mic, sisteme sigure şi cu preţuri mici.

Circuite de mică putere

Tehnologia implicată în realizarea circuitelor şi tranzistoarelor a fost pe parcursul anilor principalul mijloc de a creşte performanţele procesoarelor către frecvenţe mai mari. Relativ recent, preocuparea s-a schimbat de la frecvenţă către consumul de putere.

Ce a produs această schimbare? Până de curând, principalul aspect legat de putere, luat în considerare de către proiectanţi, era componenta de curent alternativ, cauzată de încărcarea şi descărcarea porţilor. Trecerea la tehnologia pe 90nm şi dincolo de ea, introduce o componentă puternică de curent continuu, menţionată ca pierdere sau putere statică. Într-adevăr, pierderea de curent tipică la 90nm, este în jur de 2-3 ori mai mare decât cea în cazul tehnologiei pe 130nm la aceeaşi tensiune. Această pierdere cauzează consumul a mai mult de jumătate din puterea totală a unor dispozitive pe 90nm.

Echipamentele de joasă putere sunt realizate prin procese tehnologice de putere mică, de exemplu tehnologia siliciu-pe-izolator (silicon-on-insulator – SOI). SOI reduce capacităţile parazite, rezultând o frecvenţă de comutaţie cu până la 25% mai mare sau o reducere a puterii necesare cu 20%. Se află de asemenea în lucru introducerea unui material dielectric special pentru canalele izolatoare, permiţând straturi mai subţiri, mai uşor de realizat decât straturile de dioxid de siliciu actual utilizate.

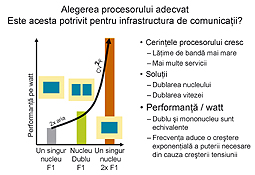

Procesoare cu nucleu dublu (Dual core processors)

Proiectanţii de circuite pentru sisteme de comunicaţii întâlnesc aceleaşi provocări legate de putere, pe care le ridică frecvenţele înalte. Dispozitivele de înaltă frecvenţă necesită tensiuni mai mari, şi din această cauză, un consum exponenţial mai mare de putere. Creşterea timpilor de întârziere, critică în cazul sistemelor în timp real, este cauzată tot de procesoarele de înaltă frecvenţă, care necesită deeper pipelines (straturi multiple) pentru alimentarea nucleului.

Ca rezultat, proiectanţii de sisteme s-au îndreptat către arhitecturi de procesoare multi-nucleu, în loc de dispozitive cu frecvenţe mai mari, pentru a permite creşterea performanţelor, minimizând creşterea consumului de putere. Microprocesoarele cu nucleu dublu, concepute iniţial pentru aplicaţii de calcul intensive, sunt acum proiectate şi lansate în aplicaţii specializate.

Suplimentar, pentru a creşte numărul de canale pe mW, aceste dispozitive cu nucleu dublu reduc lăţimea de bandă a sistemului şi latenţa sa. Controlerele de memorie on-chip, de exemplu, au îmbunătăţit latenţa de memorie de 3-4 ori.

Control mai bun al memoriilor şi pornirea de la distanţă

Memoria este de asemenea o zonă de economisire a puterii. O metodă este aceea a unui mai bun control al memoriei. Controlerele cu grad sporit de inteligenţă pentru memorii pot acum nega semnalul de tact de activare atunci când nu există transferuri către memorie, sau atunci când nu sunt prevăzute reîmprospătări ale acesteia. Această prevenire a accesării memoriei, când nu este necesar, reduce puterea consumată cu până la 20%.

O altă tehnică de proiectare pentru reducerea consumului de putere datorat memoriei şi circuitelor anexe este de a transfera boot-area şi controlul procesoarelor atunci când acestea sunt conectate împreună. Circuitul de interconectare de mare viteză, ca de exemplu tehnologia RapidIO®, permite nodurilor procesorului să fie complet controlate prin conexiunile la circuit. Aceasta elimină necesitatea de memorie Flash pentru pornire (boot-are) şi CPLD pentru comanda semnalelor de reset şi întreruperi, salvând astfel atât putere, cât şi spaţiu pe placa de circuit.

Chiar şi mecanismele ce succed, precum controlerele de Ethernet (reţea) au capacitatea de bază de a iniţia boot-area FTP fără memorie flash adiţională. Într-o aplicaţie precum DSLAM, eliminarea flash-ului pe fiecare linie, economiseşte aproximativ 3W pentru un DSLAM cu 32 de linii.

Procesoare – gestionarea economică a puterii

Proiectanţii de sisteme pot exploata oportunităţile oferite de economisirea de putere a procesoarelor, ce rezultă din concentrarea cercetărilor pentru extinderea duratei de viaţă a acumulatorilor în sistemele de calcul mobile. Comutarea dinamică a frecvenţei (Dynamic frequency switching – DFS), de exemplu, permite software-ului să schimbe rapid frecvenţa de lucru a nucleului procesorului în timpul funcţionării. Nu este nevoie de introducerea unor timpi de repaus sau de resetarea echipamentului, procesorul rămânând în toată această perioadă complet funcţional. Rezultatul este reducerea puterii consumate cu (tipic) 45%.

Pentru aplicaţiile specializate (embedded) pot fi abordate şi alte caracteristici dedicate pentru reducerea căldurii. Unele dintre noile procesoare au integrată capacitatea de gestionare dinamică a puterii (dynamic power management – DPM), care opreşte automat alimentarea unităţilor de execuţie, atunci când acestea nu sunt utilizate. Încetinirea cache-ului de instrucţiuni este un alt exemplu: reducând viteza maximă de execuţie a instrucţiunii, această tehnică maximizează impactul DPM.

Metodele de joasă putere sunt adesea trecute cu vederea şi sub-exploatate. Cu ajutorul procesoarelor de înaltă performanţă de astăzi, nu mai este vorba doar de “on” sau “off”. Noile procesoare oferă mai multe stări, precum: “run”, “doze”, “nap”, “sleep”, şi “deep” “sleep”, fiecare dintre acestea având parametri asociaţi ceasului procesorului, PLL-ului etc. Spre exemplu, este un lucru obişnuit ca, în modul “sleep” PLL să fie în starea “on”, în timp ce ceasul intern este complet oprit. În timp ce semnalele de întrerupere pot cauza tranziţii către starea de “full-on”, nu este nici un răspuns la semnalele de execuţie (snoops). O economisire majoră a puterii poate fi obţinută prin utilizarea optimă a acestor moduri, care pun procesoarele în diferite nivele de alertă şi consum de putere. Optimizarea arhitecturii software ce ia în considerare toate configuraţiile valabile, va fi complet justificată prin economisirea de energie.

Embedded Microprocessor Benchmark Consortium (EEMBC), înfiinţat în 1997, care a redefinit cu succes criteriile de performanţă ale procesoarelor, înţelege că puterea reprezintă un criteriu primar în proiectarea sistemelor specializate (embedded), verificând acum şi consumul de putere.

Până acum, proiectanţii trebuiau să se bazeze pe furnizorii de procesoare şi pe metodele lor de a măsura “puterea tipică” în anumite situaţii. Un sistem sigur, consistent şi inteligibil de stabilire a nivelelor de consum de putere, ar reprezenta un avantaj imens pentru proiectanţi. EEMBC urmăreşte măsurarea energiei consumate în timpul rulării setului existent de programe de testare a performanţelor (benchmark suites) şi apoi exprimarea rezultatelor în jouli, posibil finalizat cu un scor “PowerMark”.

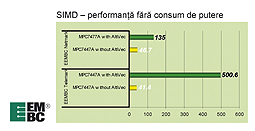

Procesare paralelă – SIMD – o singură instrucţiune, date multiple (single instruction multiple data)

Setul de instrucţiuni SIMD oferă un câştig impresionant prin creşterea semnificativă a performanţelor obţinute cu un impact minim asupra puterii.

Setul de instrucţiuni SIMD permite operaţii paralele, putându-se executa mai multe operaţii într-o sigură perioadă de tact cu ajutorul unităţilor de execuţie la nivelul instrucţiunilor, care lucrează simultan cu unităţile de calcul întreg şi cu unităţile de calcul în virgulă mobilă.

Rezultatele certificate de EEMBC arată creşterea la 12X a vitezei de prelucrare a datelor la programele de test pentru telecomunicaţii. Acestea includ algoritmuri de decodare Viterbi şi codare convoluţională.

Aceste soluţii sunt obţinute prin codificarea în C, minimizând necesitatea limbajului de asamblare. Proiectanţii evită limbajul de asamblare de câte ori este posibil, asigurând performanţă printr-un amestec de program C propriu şi biblioteci optimizate de limbaj de asamblare oferite de furnizorii de procesoare. Avantajul important al acestui set de instrucţiuni este obţinerea de performanţe ridicate cu o creştere de numai 5-10% a puterii consumate de procesor.

Alimentarea sistemelor de putere mică

Sistemele de putere joasă aduc noi provocări şi în alte aspecte ale proiectării, cum ar fi gestionarea surselor de alimentare. Reducerea dimensională a procesoarelor a dus la creşterea curentului şi micşorarea tensiunii necesare. Memoriile mai mari şi mai rapide prezintă fenomene de tranziţie mai rapide, necesitând o mai bună gestionare a puterii. Rezistenţele şi condensatoarele tradiţional folosite pe PCB pentru gestionarea curenţilor înalţi, pot conduce la o stabilizare în sarcină proastă, cu variaţii de tensiune pe placă. De asemenea, o altă problemă este datorată necesităţii mai multor tensiuni diferite pe o placă, rezultând o creştere a complexităţii traseelor de putere.

A fost acceptată o arhitectură standard, numită Point-of-Load (PoL), ce rezolvă multe dintre aceste probleme, oferind o precizie mult mai bună a tensiunii, riplu mai mic şi un răspuns tranzitoriu mai rapid. Ea asigură de asemenea şi o flexibilitate sporită, garantând interoperabilitatea dintre diferiţi furnizori.

Concluzie: Mai multe canale/mW – ATCA sau nu

Proiectanţii de structuri software şi hardware pentru comunicaţie pot utiliza o plajă largă şi în dezvoltare de unelte şi tehnici de maximizare a numărului de canale pe mW.

Aplicaţiile de acces de mare volum şi sensibile la putere, precum DSLAM şi staţiile pentru comunicaţii wireless, vor rămâne cu siguranţă în afara cadrului ATCA, putând fi costisitoare în termeni de putere, spaţiu şi bani. Pentru mulţi dintre proiectanţii de sisteme de comunicaţii, scopul este obţinerea unui consum mic de putere la un nivel de performanţă optim.

Proiectanţii de aplicaţii corespunzătoare ATCA, precum controlere pentru reţele radio (wireless radio network controllers – RNC), sunt de asemenea beneficiarii unor procesoare de joasă putere specializate şi de tehnici software pentru maximizarea canalelor de comunicaţii pe mW.

de Richard Low, Freescale Semiconductor