Perifericul “Configurable Logic Block” (CLB) din familia de microcontrolere PIC16F13145 de la Microchip Technology permite dezvoltatorilor să implementeze în hardware funcții logice discrete complexe, reducând lista de materiale (BOM) și oferind posibilitatea realizării unei logici personalizate specifice aplicației.

Limitările logicii discrete în sistemele embedded

În sistemele embedded sunt utilizate frecvent dispozitive logice discrete, precum cele din seria 74HC. Avantajul acestor circuite constă în faptul că funcționează independent de microcontroler (MCU) și pot răspunde mai rapid decât o implementare software. Pe de altă parte, aceste componente măresc lista de materiale (BOM) și necesită spațiu suplimentar pe placa de circuit imprimat (PCB).

Pentru a aborda această problemă, multe microcontrolere Microchip includ un periferic denumit CLC (Configurable Logic Cell) în gama PIC® sau un periferic similar, CCL (Configurable Custom Logic) în gama AVR®. Ambele permit implementarea unei logici personalizate configurate prin software, care poate funcționa independent de unitatea centrală de procesare (CPU). Cu alte cuvinte, odată configurată, funcția logică operează autonom, fără intervenția continuă a microcontrolerului.

Totuși, o limitare a acestor periferice este capacitatea redusă de logică disponibilă per instanță. Un CLC este aproximativ echivalent cu un singur tabel de căutare (LUT – Look-Up Table), în timp ce un CCL poate include mai multe LUT-uri independente. Aceste periferice sunt eficiente pentru implementarea unor funcții logice simple, combinarea semnalelor și integrarea cu alte periferice hardware. De exemplu, funcții precum eliminarea efectului de rebotare (debounce) a butoanelor hardware, generarea de semnale pentru LED-uri WS2812 sau decodarea în cuadratură pot fi realizate utilizând aceste resurse. Totuși, numărul limitat de instanțe disponibile restricționează complexitatea aplicațiilor.

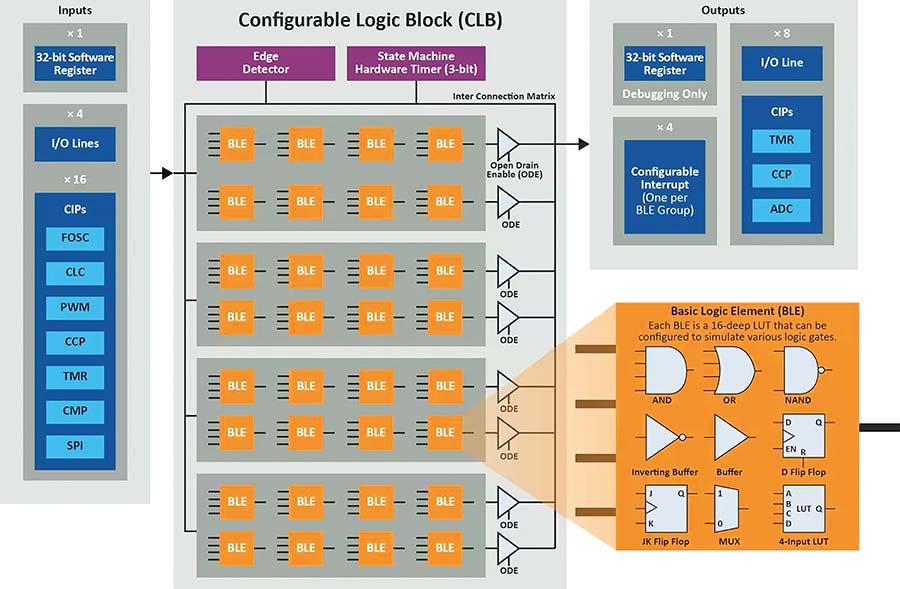

Pentru a susține aplicații mai complexe, a fost introdus un nou tip de periferic logic, Configurable Logic Block (CLB), prezentat în Figura 1, în familia de microcontrolere PIC16F13145. Este important de menționat că CLB nu înlocuiește perifericele CLC sau CCL; anumite dispozitive pot integra simultan CLC/CCL și CLB.

Arhitectura internă a blocului logic configurabil (CLB)

Blocul CLB din familia de microcontrolere PIC16F13145 este alcătuit din patru grupuri logice, fiecare conținând opt elemente logice de bază (BLE – Basic Logic Element). BLE-urile din cadrul fiecărui grup sunt interconectate, iar fiecare grup logic poate genera două ieșiri GPIO și o întrerupere opțională către CPU. La o tensiune de alimentare de 5,5 V, BLE-urile prezintă un timp de propagare tipic sub 6 ns.

Toate BLE-urile utilizează un ceas comun la nivelul întregii structuri CLB, a cărui sursă este configurabilă prin software, împreună cu un divizor de frecvență opțional. CLB poate funcționa utilizând una dintre sursele de ceas interne ale microcontrolerului sau o sursă de ceas externă.

Perifericul este inițializat din memoria microcontrolerului și poate controla direct pinii prin intermediul mecanismului PPS (Peripheral Pin Select). PPS permite realocarea pinilor I/O asociați perifericelor hardware, oferind o flexibilitate sporită în proiectare. De exemplu, dacă pinul RA1 este utilizat pentru semnalul de ceas al interfeței SPI și se dorește utilizarea pinului RA6, PPS permite remaparea acestei funcții fără modificări hardware.

Alte elemente ale CLB includ un timer hardware dedicat pe 3 biți (cu ieșiri decodate), un detector de front (edge detector) pentru semnalele de intrare și un registru de ieșire pe 32 de biți, utilizat în scopuri de depanare. De asemenea, ieșirile altor periferice independente de nucleu (CIP – Core Independent Peripheral) pot fi utilizate ca intrări pentru CLB, facilitând realizarea unor funcții logice mai complexe.

Configurarea CLB cu ajutorul CLB Synthesizer

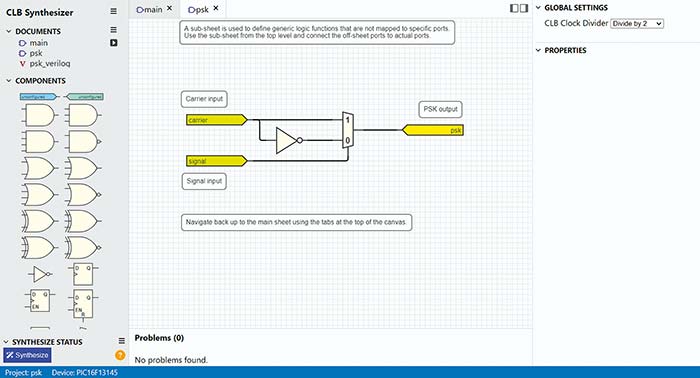

Deoarece CLB este semnificativ mai complex decât perifericele CLC sau CCL, a fost dezvoltat un instrument dedicat, denumit CLB Synthesizer. Acesta oferă o interfață grafică pentru configurarea logicii, așa cum este ilustrat în Figura 2. Pe lângă elementele logice elementare (logic primitives), instrumentul suportă și biblioteci de blocuri logice de nivel superior, care pot fi furnizate implicit sau create personalizat de utilizator.

În timpul utilizării interfeței grafice, instrumentul generează automat în fundal un modul Verilog destinat sintezei. Alternativ, dacă dezvoltatorul preferă să scrie propriul cod Verilog sau dispune deja de un fișier existent, acesta poate fi importat direct în instrument sub forma unui modul.

Figura 2: CLB Synthesizer cu exemplul Phase-Shift Keying (PSK). (Sursă imagine: Microchip Technology)

Rezultatul generat de CLB Synthesizer constă într-un fișier de asamblare ce conține fluxul de biți necesar configurării CLB-ului, precum și cod sursă pentru inițializarea acestuia ca periferic. Instrumentul poate fi utilizat fie prin intermediul MPLAB® Code Configurator (MCC), fie ca aplicație online independentă. MCC este un utilitar de generare automată a codului care permite configurarea perifericelor microcontrolerului printr-o interfață grafică. După definirea setărilor hardware, MCC generează codul de inițializare și interfața API corespunzătoare dispozitivului.

La rulare, fluxul de biți al CLB-ului este încărcat din memoria de program utilizând mecanismele hardware integrate. Un avantaj al acestei arhitecturi este posibilitatea reconfigurării CLB-ului în timpul execuției aplicației, prin încărcarea unui flux de biți alternativ stocat în memoria dispozitivului.

Exemple de utilizare

Pentru a demonstra funcționarea CLB-ului în aplicații reale, au fost dezvoltate mai multe exemple de utilizare. În continuare sunt prezentate două dintre acestea: convertorul pentru afișaj cu 7 segmente și aplicația SPI către WS2812. Aceste exemple reprezintă blocuri funcționale reutilizabile, care pot fi integrate într-o soluție completă. Scopul lor este de a evidenția utilitatea perifericului CLB și valoarea pe care acesta o poate aduce într-un proiect.

Convertor pentru afișaj cu 7 segmente

Primul exemplu constă într-un convertor pentru afișaj cu 7 segmente. Afișajele cu 7 segmente pot fi controlate prin intermediul pinilor standard de intrare/ieșire (I/O), însă o implementare convențională necesită, de regulă, o tabelă de căutare definită în software pentru a converti valoarea de intrare în modelul corespunzător de activare a segmentelor. În această implementare, CLB-ul funcționează ca o tabelă de căutare hardware.

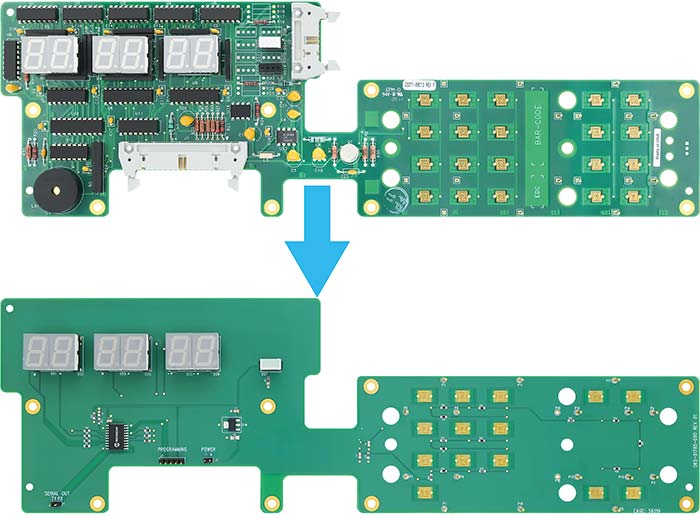

Figura 3: Comparație între PCB-ul original și noul ansamblu. Exemplu dezvoltat de Josh Booth. (Sursă imagine: Microchip Technology)

Caracterul dorit (de la 0 la F) este încărcat în registrul de intrare al CLB-ului din software, iar fiecare segment al afișajului este controlat de un LUT care mapează combinațiile de intrări la ieșiri.

Acest exemplu a fost utilizat intern pentru dezvoltarea unei noi plăci de control destinate unui sistem de cronometrare. Interfața originală cu utilizatorul, proiectată în anii 1980, era bazată pe logică discretă din seria 74HC. Prin utilizarea CLB, un singur microcontroler cu 20 de pini poate implementa atât logica afișajului, cât și logica tastaturii prezente pe placă, reducând semnificativ lista de materiale (BOM). O comparație între cele două soluții este prezentată în Figura 3.

Convertor SPI către WS2812

Următorul exemplu prezintă un convertor SPI către WS2812. Protocolul WS2812 este un protocol serial pe un singur fir, utilizat pentru controlul matricelor de LED-uri prin modulație în lățime de impuls (PWM – Pulse Width Modulation). În această implementare, perifericul SPI este utilizat ca registru de deplasare pentru datele transmise către LED-uri, iar CLB convertește semnalele SCLK și SDO în forma de undă necesară pentru protocolul WS2812.

Configurare ceas SPI

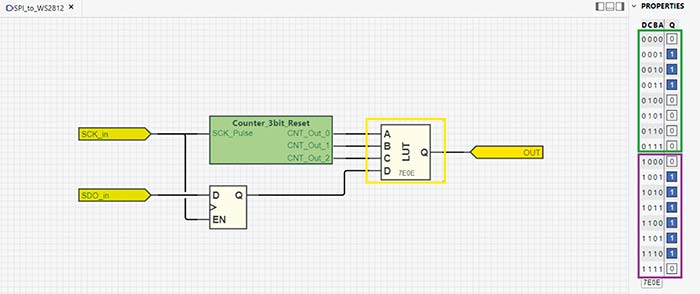

Implementarea utilizează un contor pe 3 biți declanșat la frontul descendent al semnalului SCLK, un latch de tip D cu semnal de activare și un LUT cu 4 intrări, așa cum este ilustrat în Figura 4. Elementul esențial al acestei soluții îl reprezintă relația dintre sursele de ceas ale SPI și CLB. Ceasul SPI este configurat cu nivel HIGH în stare inactivă și comută la frontul ascendent, funcționând la frecvența semnalului WS2812 (800 kHz), în timp ce sursa de ceas a CLB operează la o frecvență de zece ori mai mare (8 MHz).

Figura 4: Diagrama bloc a convertorului SPI către WS2812, dezvoltată de Petre Teodor-Emilian. (Sursă imagine: Microchip Technology)

Atunci când SCLK este în nivel LOW, contorul pe 3 biți este declanșat și începe să numere. Când valoarea ajunge la 7 (0b111), contorul se oprește și rămâne la 0 până la următoarea perioadă LOW a semnalului de ceas.

Ieșirea contorului este aplicată unui LUT cu 4 intrări, împreună cu datele memorate în latch. Această combinație determină forma finală a impulsului transmis, vizibilă în partea dreaptă a Figurii 4. După resetarea contorului, ieșirea acestuia rămâne la 0 pentru a finaliza ciclul curent. Ulterior, următorul octet este transmis prin perifericul SPI, iar procesul se repetă.

Ambele exemple evidențiază avantajele implementării logicii discrete în interiorul unui microcontroler. Perifericele hardware independente descarcă sarcini de la CPU, ceea ce poate conduce la timpi de răspuns îmbunătățiți și la reducerea consumului de energie, diminuând în același timp numărul de componente externe. CLB permite dezvoltarea unor aplicații complexe care anterior erau dificil sau imposibil de implementat exclusiv în cadrul unui microcontroler.

În prezent, perifericul CLB este disponibil în familia de microcontrolere PIC16F13145, oferită de Microchip Technology prin Microchip Direct și alți distribuitori autorizați.

Autor:

Robert Perkel, Inginer de aplicații, Divizia de microcontrolere pe 8 biți, Microchip Technology

Robert Perkel este inginer de aplicații în cadrul Microchip Technology. În această funcție, el dezvoltă conținut tehnic, inclusiv note de aplicații, articole și materiale video. De asemenea, este implicat în analiza cazurilor de utilizare a perifericelor, dezvoltarea de exemple de cod și realizarea de demonstrații tehnice. Perkel este absolvent al Virginia Tech, unde a obținut o diplomă de licență în inginerie informatică.

Robert Perkel este inginer de aplicații în cadrul Microchip Technology. În această funcție, el dezvoltă conținut tehnic, inclusiv note de aplicații, articole și materiale video. De asemenea, este implicat în analiza cazurilor de utilizare a perifericelor, dezvoltarea de exemple de cod și realizarea de demonstrații tehnice. Perkel este absolvent al Virginia Tech, unde a obținut o diplomă de licență în inginerie informatică.

Microchip Technology | https://www.microchip.com

![]()

Glosar de termeni

CLB (Configurable Logic Block) – Periferic hardware avansat integrat în anumite microcontrolere PIC, care permite implementarea de funcții logice complexe direct în hardware, independent de CPU.

CLC (Configurable Logic Cell) – Periferic logic configurabil disponibil pe unele microcontrolere PIC, utilizat pentru implementarea de funcții logice simple definite prin software.

CCL (Configurable Custom Logic) – Echivalent al CLC pe microcontrolerele AVR, care permite realizarea de funcții logice personalizate în hardware.

BLE (Basic Logic Element) – Element logic elementar din structura CLB, utilizat pentru implementarea funcțiilor logice configurabile.

LUT (Look-Up Table) – Tabel de căutare utilizat pentru maparea combinațiilor de intrări la ieșiri logice.

PPS (Peripheral Pin Select) – Mecanism care permite remaparea funcțiilor periferice pe diferiți pini I/O ai microcontrolerului.

CIP (Core Independent Peripheral) – Periferic hardware care poate funcționa independent de nucleul CPU.

WS2812 – Protocol serial pe un singur fir utilizat pentru controlul LED-urilor adresabile RGB prin modulație PWM.

SPI (Serial Peripheral Interface) – Interfață serială sincronă utilizată pentru comunicarea între microcontroler și periferice externe.

PWM (Pulse Width Modulation) – Tehnică de control al puterii prin variația lățimii impulsurilor.