Clienții finali se așteaptă ca dispozitivele electronice și alte dispozitive mobile să ofere atât răspuns rapid, cât și o funcționalitate deosebită – toate acestea însoțite de o durată de viață mai mare a bateriei. Totuși, pentru dezvoltatori, cerințele de răspuns în timp real și performanțele ridicate din multe aplicații, au condus la utilizarea de procesoare separate, cu scopul de a servi aceste solicitări aflate în conflict. Acest lucru aduce după sine un plus de cost, energie, spațiu, precum și o complexitate a nivelului hardware și software.

O mai bună abordare ar fi integrarea hardware-ului necesar într-un singur cip. Astfel apar dispozitivele de procesare multi-nucleu HMP (heterogeneous multicore processing). Conținând mai multe nuclee de diferite tipuri, aceste procesoare pot oferi avantaje de optimizare a performanțelor, reducerea consumului energetic și îmbunătățirea securității și siguranței în funcționare a sistemului.

Acest articol descrie modalitatea prin care dezvoltatorii pot utiliza procesoarele eterogene multi-nucleu de la NXP Semiconductors pentru a răspunde cerințelor acestor sarcini de lucru mixte fără compromiterea cerințelor de joasă putere și complexitate redusă a designului.

Schimbarea cerințelor

Progresele în ceea ce privește tehnologiile senzoriale și algoritmii de procesare a datelor au creat oportunități semnificative pentru dezvoltatori în a gestiona cerințele aflate în conflict, precum achiziția de date în timp real și executarea de algoritmi de calcul intensiv. În trecut, în mod tipic, dezvoltatorii împărțeau aceste sarcini de lucru în sisteme separate.

La cel mai jos nivel al ierarhiei de rețea, procesoarele embedded, precum cele bazate pe nucleu Arm® Cortex®-M4 colectau date, rulând un program optimizat pe un sistem de operare în timp real (RTOS). La un nivel mai ridicat al ierarhiei, procesoarele de aplicații de înaltă performanță, precum cele bazate pe nucleu Arm Cortex-A7 executau în schimb algoritmi de analiză de date, rulând programe de aplicații pe sisteme de operare familiare precum Linux sau Android.

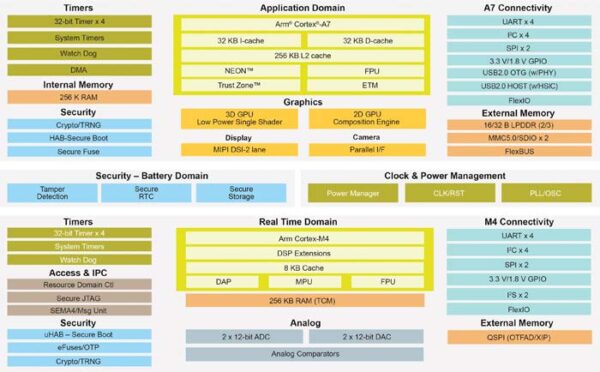

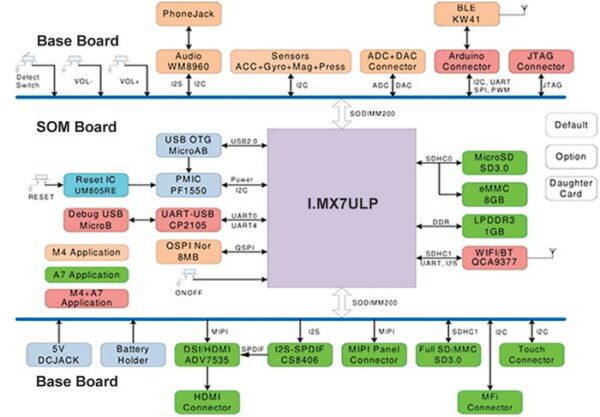

Figura 1: Pe lângă o paletă largă de module și periferice, familia de procesoare de aplicație NXP i.MX 7ULP combină un nucleu Arm Cortex-M4 pentru procesare în timp real cu un nucleu Arm Cortex-A7 pentru procesare de aplicații. Aceasta utilizează domenii de putere separate pentru optimizarea consumului de putere și performanței. (Sursă imagine: NXP)

Apariția sistemelor de calcul la margine (edge computing systems) a mutat execuția programului de aplicație mai aproape de sursa de date. De fapt, solicitarea pentru un răspuns mai rapid de la algoritmi de analiză mai complecși a împins cerințele de procesare a aplicației exact în dispozitivele finale. Din ce în ce mai mult, utilizatorii se așteaptă la capabilități de analiză sofisticate, inclusiv la elemente de inteligență artificială, care să fie integrate în dispozitive precum senzori IoT, dispozitive purtabile și alte produse cu un consum scăzut de putere.

Rolul procesării multi-nucleu eterogene

Emergența dispozitivelor HMP care combină nuclee de procesoare embedded și de aplicație i-a ajutat pe dezvoltatori să gestioneze mai eficient sarcini de lucru mixte în numeroase aplicații. Procesoarele HMP integrează diferite nuclee, fiecare optimizat pentru a răspunde unor cerințe diferite asociate cu sarcinile de lucru ale produsului țintă. Cu ajutorul familiei NXP i.MX 7ULP (ultra-joasă-putere) dezvoltatorii pot utiliza capabilitățile de performanță ale unei arhitecturi HMP pentru a răspunde cerințelor lipsite de compromis ale clienților pentru performanță ridicată și durată mare de viață a bateriei oferite de noua generație de produse ULP.

Fiind disponibile în ambele versiuni – utilizare casnică (MCIMX7U5DVP07SC) și industrială (MCIMX7U5CVP06SC) – procesoarele i.MX 7ULP integrează nucleele lor eterogene cu unități de procesare grafică, acceleratoare de securitate, controlere de memorie și un set complet de interfețe periferice (Figura 1).

Dezvoltată special pentru proiecte portabile cu restricții de consum energetic, familia NXP i.MX 7ULP se adresează cerințelor emergente de combinare a unui nucleu Arm Cortex-A7 cu un nucleu Cortex-M4, fiecare alimentat de un domeniu de putere separat. Suplimentar, utilizarea de diverse insule de putere permite ca module diferite să fie nealimentate atunci când nu este necesar. După cum se va vedea mai jos, caracteristicile complexe de management energetic integrate în dispozitivele i.MX 7ULP permit dezvoltatorilor să utilizeze aceste domenii și insule de putere pentru a regla performanțele și consumul energetic, pentru a se potrivi aplicațiilor.

Optimizare energetică

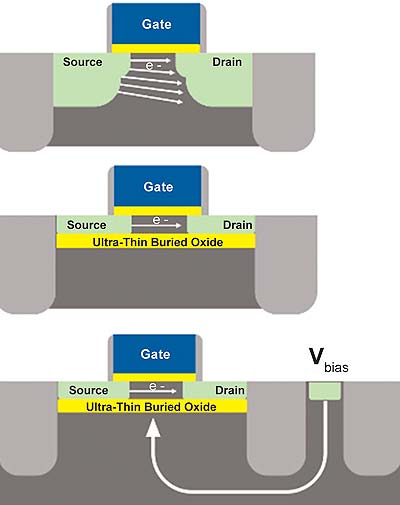

Figura 2: Un tranzistor convențional poate avea o pierdere considerabilă, datorită circulației electronilor de la sursă la drenă (sus), dar familia NXP i.MX 7ULP este fabricată cu un strat îngropat de oxid ultrasubțire, care împiedică fluxul de electroni (mijloc) și o structură care mărește vitezele sau încetinește fluxul de electroni cu polarizare directă (FBB) sau polarizare inversă (RBB) (jos). (Sursă imagine: NXP)

Atunci când proiectul vostru se bazează pe familia i.MX 7ULP, trebuie să știți că NXP a integrat în dispozitive caracteristici de optimizare a puterii și performanței de la nivelul de proiectare al cipului până la arhitectură.

La nivelul cel mai fundamental, familia i.MX 7ULP combină metodele de fabricație, care reduc pierderile de curent cu geometriile tranzistorului, care diminuează pierderile parazite, micșorând, astfel, consumul energetic dinamic. Spre deosebire de structurile cu tranzistoare convenționale (Figura 2, sus), dispozitivele i.MX 7ULP sunt fabricate cu un strat îngropat de oxid, ultrasubțire (Figura 2, mijloc), care reduce fluxul de electroni de la sursă la drenă, reducând astfel pierderile de curent; o îmbunătățire suplimentară permite proiectanților să adauge o polarizare directă (FBB – forward body bias) sau o polarizare inversă (RBB – reverse body bias) (Figura 2, jos).

Atunci când randamentul energetic este o prioritate de top, dezvoltatorii pot utiliza RBB pentru a reduce fluxul de electroni și pentru a reduce și mai mult pierderea de curent și consumul general al dispozitivului, cu prețul unor performanțe mai reduse. În mod invers, dezvoltatorii pot utiliza FBB, care îmbunătățește fluxul de electroni, pentru a îmbunătăți performanțele, cu costul unui consum energetic crescut, datorită pierderilor mai mari de curent.

La nivelul de proiectare al cipului, familia i.MX 7ULP încorporează tehnici multiple incluzând scalare dinamică a frecvenței (DFS – dynamic frequency scaling) și scalare dinamică a tensiunii (DVS – dynamic voltage scaling), porți de ceas și de putere bazate pe software. Pe lângă reducerea consumului energetic al diferitelor periferice, dezvoltatorii pot utiliza aceste caracteristici pentru a închide selectiv blocuri de memorie internă sau să plaseze memoria în diferite stări de economie energetică.

La nivel arhitectural, abilitatea de a regla puterea și performanțele este extinsă mai mult prin utilizarea de domenii de putere multiple, incluzând domeniile de putere separate, menționate anterior pentru subsistemele Cortex-A7 și Cortex-M4.

Fiecare dintre domeniile de putere ale nucleelor de procesor includ drivere FBB și RBB, stabilizatoare dedicate LDO, dispozitive de monitorizare detector de nivel ridicat (HVD – high level detector) și detector de nivel scăzut (LVD – low level detector) proiectate pentru a semnaliza variațiile tensiunii de alimentare peste sau sub pragurile proiectate. Un monitor separat PoR (power-on-reset) urmărește nivelul tensiunii în domeniul de putere de tipul ”mereu pornit”.

Împreună cu domeniile de putere separate ale nucleelor, domeniile de putere individuală controlează, de asemenea, funcții de sistem precum hardware de tip mereu pornit, în vreme ce un domeniu de putere alimentat de la baterii gestionează alimentarea unor funcții critice ce includ, printre altele ceasul de timp real și un modul de stocare de siguranță nevolatil. Precum în cazul domeniilor de putere ale nucleelor, fiecare dintre aceste domenii specializate, suportă un set cuprinzător de funcții de economie energetică (care sunt prea multe pentru a fi detaliate într-un singur articol).

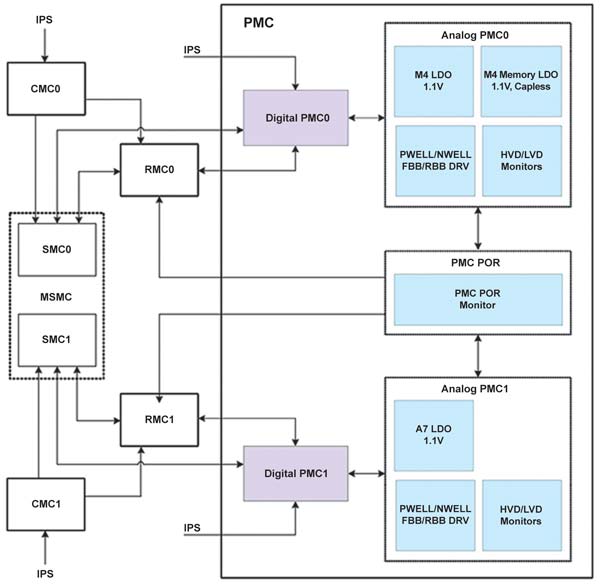

Figura 3: Familia NXP i.MX 7ULP integrează o capabilitate de control complexă ce permite dezvoltatorilor să configureze programat domeniile de putere și insulele de putere pentru a regla puterea și performanțele în vederea respectării cerințelor schimbătoare ale aplicațiilor. (Sursă imagine: NXP)

Pentru a lua un exemplu, domeniul de putere pentru funcționalitatea mereu pornit include un modul de activare cu pierdere redusă LLWU (Low-Leakage Wake-Up Unit), care permite dezvoltatorilor să utilizeze pini externi multipli sau module interne ca surse de activare pentru moduri speciale de putere cu pierderi reduse descrise mai jos.

Aceste funcții arhitecturale sunt legate împreună într-un controler de management energetic integrat al modulului (PMC – power management controller) care gestionează aceste domenii separate de putere și insulele de putere ale dispozitivului (Figura 3).

În această abordare, dezvoltatorii inițiază tranziții ale modului de putere prin trimiterea de comenzi pe magistrala subsistemului periferic inteligent (IPS – intelligent peripheral subsystem) către un control complex ce conține trei module strâns legate:

- Controler mod nucleu (CMC – Core Mode Controller), care suportă funcții de nucleu multiple

- Controler mod sistem multi-nucleu (MSMC – Multicore System Mode Controller), conținând controler de mod sistem 0 (SMC0) pentru domeniul de putere al Cortex-M4 și SMC1 pentru domeniul de putere al Cortex-A7, care gestionează secvențierea între diferitele moduri de putere, monitorizează evenimentele utilizate pentru inițializarea tranzițiilor de moduri de putere și controlează în mod general funcțiile de putere, ceas și memorie asociate cu optimizarea de putere.

- Controler mod de reinițializare (RMC – Reset Mode Controller), care gestionează funcțiile de reinițializare ale cipului.

Reglarea puterii și a performanței

Pentru toate capabilitățile de management energetic, familia i.MX 7ULP prezintă un model de programare familiar pentru dezvoltatori. Precum și în cazul altor procesoare avansate, dispozitivele i.MX 7ULP ating diferite stări de operare de joasă putere printr-o serie de moduri programabile de joasă putere. De fapt, nucleul procesorului i.MX 7ULP suportă câteva moduri de joasă putere controlabile software, care permit dezvoltatorilor să reducă consumul energetic la nivelul cel mai mic posibil pentru funcționalitatea necesară.

Prin utilizarea acestor moduri diferite de joasă putere, dezvoltatorii pot pregăti unul sau ambele nuclee și subsistemele lor în diferite variante ale unui mod normal de rulare RUN, mod de așteptare WAIT și mod de oprire STOP.

Modul de rulare normală RUN și modul de mare viteză HSRUN oferă operare de înaltă performanță pentru a asigura suport porțiunilor de calcul intensiv ale unei aplicații. În modul HSRUN, subsistemul nucleu operează la frecvența sa cea mai ridicată. Dacă aplicația poate tolera performanțe mai reduse, dezvoltatorii pot stabili nucleul în mod de rulare de foarte joasă putere VLPR (Very Low Power Run) pentru operare la o frecvență maximă de 48 MHz, cu consum energetic redus corespunzător.

În modul de așteptare WAIT, perifericele operează complet, dar nucleul depinde de o poartă de ceas, așteptând într-o stare statică, dar gata de a se activa la primirea unui semnal WFI (Wait-For-Interrupt). Cu acest mod, dezvoltatorii pot lăsa autonomă operarea perifericelor, utilizarea bufferelor sau a tranzacțiilor de acces direct la memorie (DMA) până la apariția unei întreruperi care scoate nucleul din starea de așteptare WAIT. Modul de așteptare de foarte joasă putere VLPW (Very Low Power Wait) permite perifericelor să continue operarea la frecvență redusă, dar cu controlul porții ceasului nucleului.

În aplicații precum dispozitive purtabile sau portabile, sistemul poate avea perioade extinse de inactivitate, întrerupte periodic de o creștere a activității. În aceste cazuri, abilitatea de a economisi energie este critică pentru durata de viață a bateriei. Atunci când aplicația poate tolera un timp mai redus de activare pentru nucleu, abilitatea de a plasa dispozitivul în stări de inactivitate mai profunde (sleep) decât RUN, WAIT, sau variantele lor de foarte joasă putere, oferă o opțiune eficientă. Pentru a asigura suport acestei abordări, dezvoltatorii pot plasa fiecare subsistem nucleu i.MX 7ULP într-o stare de adormire profundă pentru care sunt posibile diferite valori de timpi de activare:

- În starea STOP, unele periferice pot opera asincron, dar nucleul rămâne în stare statică cu timpi de activare de 7 microsecunde (μs) pentru Cortex-A7 sau 7 μs pentru Cortex-M4

- În modul de oprire de foarte joasă putere (VLPS – In Very Low Power Stop), operațiile perifericelor sunt limitate mai mult, dar nucleul rămâne în stare statică, având timpi de activare de 21.5 μs (Cortex-A7) sau 9 μs (Cortex-M4).

Pentru aplicații cu și mai multe cerințe stringente de putere, dezvoltatorii pot stabili pentru fiecare nucleu următoarele moduri speciale cu pierderi reduse care închid mai multe subsisteme ale dispozitivului:

- Oprire cu pierderi reduse (LLS – Low Leakage Stop), pentru care ceasul controlează nucleul, magistrala și perifericele, lăsând nucleul în stare WFI, conducând la un timp de activare de 40 μs (Cortex-A7) sau 58 μs (Cortex-M4)

- Oprire cu pierderi foarte reduse (VLLS – Very Low Leakage Stop), la care ceasul controlează întreg domeniul de putere al nucleului, conducând la timpi extinși de activare, de 60 μs pentru Cortex-A7 sau 375 μs pentru Cortex-M4

Pentru economii energetice chiar și mai mari, dezvoltatorii pot utiliza RBB în unele moduri de putere, incluzând aici VLPS și LLS cu o reducere corespunzătoare în performanță și o creștere incrementală în ceea ce privește timpul de activare, cu aproximativ 2 până la 4 μs.

În schimb, atunci când este nevoie de sarcini de lucru cu calcule intensive, dezvoltatorii pot rula nucleele într-un mod special de mare viteză (HSRUN – high speed run). Acesta schimbă frecvența de operare a Cortex-A7 de la valoarea sa normală de 500 MHz la un mod de supra-conducere ce rulează la 720 MHz.

Cu ajutorul acestui nivel fin de control, dezvoltatorii pot configura i.MX 7ULP să respecte chiar și cele mai extreme cerințe de putere, fără a sacrifica funcționalități esențiale. De exemplu, o aplicație poate avea nevoie de cel mai mic consum energetic posibil, dar necesită funcționalitatea de timp real a nucleului Cortex-M4, precum părți și utilizarea unor părți specifice de periferie sau memorie ale subsistemului Cortex-A7. În acest caz, dezvoltatorul poate plasa subsistemul Cortex-A7 în starea STOP sau VLPS, accesând memoria sa sau perifericele din Cortex-M4, după cum nucleul execută operațiile sale de timp real. Pentru mai multe economii energetice, dezvoltatorii pot utiliza ceasul Cortex-M4 pentru a comanda perifericele Cortex-A7.

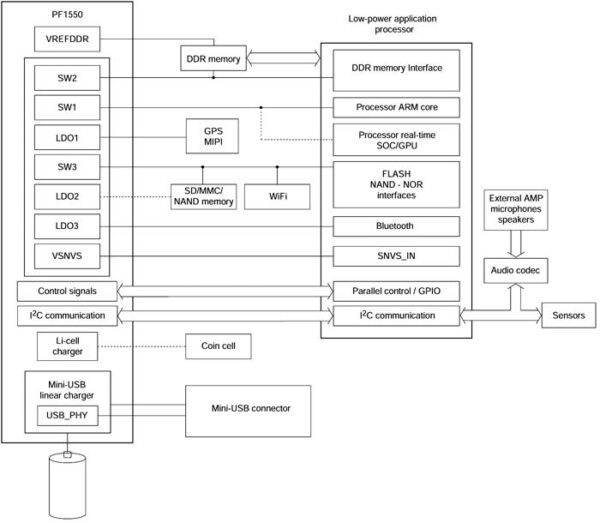

Figura 4: Circuitul integrat de management energetic NXP MC32PF1550A3EPR2 oferă un set complet de surse de alimentare solicitate de procesorul NXP i.MX 7ULP, reducând proiectarea hardware la o combinație directă a acestor 2 dispozitive și câteva componente pasive. (Sursă imagine: NXP)

Implementare simplă a sistemului

Pentru a implementa un sistem de joasă putere cu i.MX 7ULP, dezvoltatorii pot alege dintre modurile de putere programabile software și dintre configurațiile disponibile pentru o potrivire cât mai bună la cerințele de putere și performanță. Pe partea hardware, proiectarea sistemului este chiar mai simplă.

Pentru aplicații tipice, dezvoltatorii pot în mod simplu să combine un procesor i.MX 7ULP cu companionul său, circuitul integrat de management energetic (PMIC) NXP MC32PF1550A3EPR2 pentru a completa un design capabil de a gestiona sarcini mixte fără a compromite bugetele limitate de putere (Figura 4).

Figura 5: Kit-ul de evaluare MCIMX7ULP-EVK combină o placă sistem pe modul conținând un procesor i.MX 7ULP și MC32PF1550A3EPR2 PMIC cu o placă de bază ce conține senzori, conectori și alte componente necesare pentru a grăbi dezvoltarea software cu dispozitivele i.MX 7ULP. (Sursă imagine: NXP)

Proiectat special pentru a suporta cerințele de alimentare ale procesoarelor NXP precum cele ale familiei i.MX 7ULP, MC32PF1550A3EPR2 integrează trei stabilizatoare în mod de comutație coborâtoare de tensiune (SW1, SW2, SW3), trei regulatoare LDO (LDO1, LDO2, LDO3), o sursă de tensiune de referință pentru memorie, un încărcător pentru baterii cu litiu cu o singură celulă și o memorie programabilă o singură dată (OTP – one-time programmable) pentru configurarea dispozitivului.

Cu ajutorul kit-ului de evaluare MCIMX7ULP-EVK, NXP demonstrează interfața hardware directă necesară pentru a combina MC32PF1550A3EPR2 PMIC cu dispozitivul i.MX 7ULP. Împreună cu o placă sistem pe modul (SOM – system-on-module) conținând procesorul i.MX 7ULP și MC32PF1550A3EPR2 PMIC, kit-ul include o placă de bază cu senzori multipli, capabilitate wireless, un codec audio, un conector SD și mulți alți conectori, inclusiv JTAG și Arduino (Figura 5).

În timp ce kit-ul de evaluare oferă funcționalitate imediat după scoaterea din cutie, NXP oferă, de asemenea, dezvoltatorilor posibilitatea de a descărca fișiere de proiectare, unelte și pachete suport placă pentru software particular utilizând FreeRTOS pentru programare în timp real și Linux sau Android pentru programare de aplicații.

Concluzie

Necesitatea pentru funcționalitate complexă și durată mai mare de viață a bateriilor în cadrul produselor mobile i-a forțat pe dezvoltatori în mod tradițional la un anume nivel de compromis între consum energetic și performanță. De asemenea, creșterea așteptărilor de la datele funcție de timp de la mai mulți senzori în cadrul dispozitivelor IoT, purtabile și alte dispozitive portabile a condus la un alt compromis între capabilitățile de timp real și performanțele la nivel de aplicație.

Totuși, după cum s-a putut observa, dezvoltatorii se pot orienta către arhitecturi HMP, precum cele utilizate în cadrul familiei de procesoare i.MX 7ULP de la NXP pentru a răspunde cerințelor stringente de ultra joasă putere fără sacrificarea capabilităților.

Autor: Rich Miron – Inginer de aplicații

Autor: Rich Miron – Inginer de aplicații

Rich Miron, Inginer de aplicații la Digi-Key Electronics, face parte din grupul de autori care crează articole tehnice (Technical Content Group) din 2007, având responsabilitatea principală de a scrie și edita articole, bloguri și module de instruire pentru cunoașterea produselor.

Înainte de Digi-Key, el a testat și calificat sisteme de control și instrumentare pentru submarine nucleare. Rich deține o diplomă în inginerie electrică și electronică de la Universitatea de Stat din North Dakota din Fargo, ND.

Digi-Key Electronics | https://www.digikey.com