Stabilizatoarele cu cădere mică de tensiune – LDO (Low Dropout Regulators) reprezintă circuite de bază în aplicaţii embedded cu microcontroler. Pentru proiectare, unde simplitatea, flexibilitatea, spaţiul ocupat şi costul sunt preocupări primare, LDO reprezintă soluţia optimă de alimentare. Aplicaţiile ţintă includ aplicaţii industriale şi de întreprindere, precum circuite de control industriale, post stabilizatoare pentru surse în comutaţie (SMPS), plăci server şi produse de larg consum, ca de exemplu sisteme audio/video şi STB (Set Top Boxes).

Una dintre caracteristicile uzuale ale aplicaţiilor embedded este alimentarea cu tensiune alternativă, fie de la o sursă AC industrială multifazată, fie de la sursa AC uzuală 110V/220V 50Hz/60Hz. Tensiunea alternativă este apoi redresată într-o tensiune înaltă continuă, precum 12V sau 24V, care este apoi convertită în tensiuni continue mai mici. Această conversie DC/DC este în mod tipic realizată de un stabilizator coborâtor de tensiune pentru a maximiza randamentul energetic al conversiei. Tensiunea continuă mică, cu valorile cele mai utilizate de 3,3V şi 5V, reprezintă sursa de alimentare sau sursa sistemului pentru circuitele embedded. Majoritatea microcontrolerelor de astăzi sunt alimentate la tensiuni între 1,8V şi 5V, care sunt tipic convertite din sursa sistemului prin dispozitive economice LDO.

Suplimentar faţă de executarea funcţiilor de nivel de aplicaţie, microcontrolerele embedded acţionează ca “supervizori de sistem” executând sarcini precum monitorizarea şi gestionarea energiei sistemului. Din această cauză, LDO trebuie de asemenea să ofere microcontrolerului informaţii relevante despre starea energetică cu scopul de a-l ajuta la luarea de decizii de comandă privitoare la sistem, de a fi controlabil de către microcontrolerul embedded pentru a reacţiona la schimbări ale stării sistemului.

De aceea, suplimentar curentului de sarcină, care este întotdeauna primul parametru care trebuie luat în considerare de proiectanţi, mai sunt câteva caracteristici şi specificaţii care sunt considerate critice în aplicaţii embedded, incluzând căderea de tensiune (dropout voltage), un indicator al stării energetice a microcontrolerului, precum ieşirea de “power good” şi o caracteristică de feedback, precum shutdown.

Este întotdeauna considerată o bună practică, alegerea unui LDO cu căderea cea mai mică de tensiune, pentru că ea oferă cea mai mare flexibilitate şi toleranţă la erori. De exemplu, în numeroase aplicaţii embedded, tensiunea de 3,3V de la sursa sistemului este convertită descrescător la 2,5V, lăsând numai maxim 800mV pentru căderea de tensiune pe un domeniu mare de temperatură (exemplu de la -40°C la 125°C). Aceasta înseamnă o cădere tipică de tensiune în condiţii normale (25°C) de maxim 300mV.

Ieşirea de indicare a energiei “Power good” este de asemenea critică, deoarece microcontrolerul embedded are nevoie să îndeplinească anumite funcţii de administrare energetică drept răspuns direct la informaţiile privind fluctuaţiile nivelelor energetice. Într-o aplicaţie embedded ce converteşte tensiunea sistemului de 3,3V în 2,5V, dacă de exemplu tensiunea sistemului scade la 2,8V, nu mai este suficientă plaja de cădere de tensiune pentru păstrarea stabilizării la 2,5V. Atunci când apar asemenea condiţii, ieşirea cu privire la situaţia energetică “power good” atenţionează microcontrolerul embedded. Deoarece, în astfel de situaţii, răspunsul cel mai folosit de microcontrolerul embedded este de a reseta sistemul, este necesară o întârziere programabilă pe ieşirea “power good”, cu scopul de a optimiza temporizarea resetării sistemului.

O altă caracteristică critică a LDO este necesitatea de a putea fi închise, fie la comanda microcontrolerului embedded, fie la comanda altui nivel de inteligenţă al sistemului. Aceasta se datorează faptului că, atunci când microcontrolerul embedded decide să închidă sistemul, fie voluntar, fie ca răspuns la nişte condiţii de eroare, LDO trebuie să fie închis pentru a economisi energie şi pentru a preveni apariţia unor posibile avarii.

Punând toate aceste elemente împreună, un LDO ideal pentru aplicaţii tipice embedded trebuie să aibă următoarele caracteristici critice incluse într-o singură capsulă:

• Curent de sarcină ridicat, până la 1A;

• Cădere de tensiune mică, tipic mai puţin de 300mA;

• Ieşire “Power good” cu întârziere programabilă;

• Intrare de comandă de închidere.

Un exemplu de soluţie ideală de LDO este MCP1726 de la Microchip Technology. MCP1726 este primul LDO din industrie special proiectat pentru aplicaţii embedded cu toate caracteristicile de mai sus incluse într-un singur cip, incluzând curent de sarcină de 1A, cădere de tensiune tipică de 150mV, ieşire de “Power Good” cu întârziere programabilă de către utilizator şi intrare de comandă a închiderii.

LDO – Stabilizare, stabilitate şi compensare

Articolul de faţă doreşte să reprezinte o privire practică şi directă asupra stabilizării, stabilităţii şi compensării LDO, incluzând ecuaţiile şi exemplele necesare inginerilor proiectanţi cu experienţă şi nivele de educaţie diferite.

Pentru început vor fi trecute în revistă cele trei elemente cheie ale unui stabilizator liniar “generic”:

1. un element de trecere (pass element)

2. un domeniu de tensiune de referinţă (bandgap reference)

3. un amplificator de eroare (error amplifier)

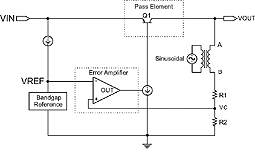

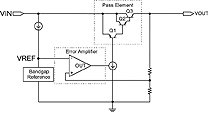

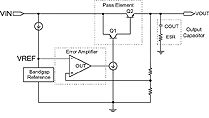

Stabilizarea tensiunii de ieşire a stabilizatoarelor liniare este realizată prin reacţie inversă. Pentru ilustrarea conceptului de reacţie inversă (feedback), se va utiliza ca exemplu un stabilizator cu tranzistor PNP (Figura 1.a, fără transformator de cuplare).

Divizorul rezistiv, amplificatorul de eroare şi elementul de trecere cu tranzistor PNP formează o buclă închisă. Tensiunea de ieşire, VOUT, oferă o tensiune de reacţie inversă prin divizorul rezistiv, VC = VOUT * R2/ (R1 + R2), către intrarea neinversoare a amplificatorului de eroare. Tensiunea de ieşire de referinţă (VREF) este o tensiune fixă de înaltă precizie, care este legată la intrarea inversoare a amplificatorului de eroare. Amplificatorul de eroare este, în esenţă, un amplificator operaţional, care-l face pe VC egal cu VREF prin furnizarea unui curent de masă către baza tranzistorului PNP. Tranzistorul PNP, în schimb, furnizează suficient curent de ieşire pentru a menţine VOUT la o valoare fixă. O fracţiune din această valoare, VC, este egală cu VREF. Tensiunea de ieşire stabilizată este definită, deci, ca:

VOUT = VREF x (1 + R1/R2) (1)

Această ecuaţie ilustrează că reacţia inversă este negativă şi că reglarea tensiunii de ieşire rezultând din această reacţie, are polaritate opusă faţă de schimbarea “originală” a tensiunii de ieşire. În aplicaţiile reale, este necesară o reacţie inversă negativă suficientă pentru ca bucla închisă să rămână stabilă.

De exemplu, să ne imaginăm o mică perturbare introdusă în buclă. Cuplarea printr-un transformator a unui mic semnal sinusoidal la tranzistorul de trecere PNP modelează această perturbare (Figura 1.a).

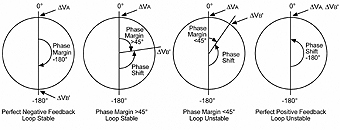

Iniţial, semnalul cel mic are valoarea DVA în punctul A, şi valoarea DVB în punctul B. Semnalul din punctul B trece prin buclă şi ajunge în punctul A cu valoarea DVB’. Cu toate că DVA şi DVB’ au aceeaşi mărime, există o diferenţă de fază între cele două semnale.

Pentru simplificarea analizei noastre, considerăm că amplificatorul de eroare introduce o reacţie inversă “perfect” negativă în buclă. Aceasta înseamnă că, dacă în bucla de reacţie inversă ar fi numai eroarea de amplificare DVA, acesta ar fi defazat faţă de DVB’ cu -180° (Figura 1.b). Oricum, din cauza capacităţii interne a elementului de trecere, apare o defazare care reduce acest perfect -180° cu o valoare între 0° şi -180° (sens trigonometric cu -180° ca punct de pornire).

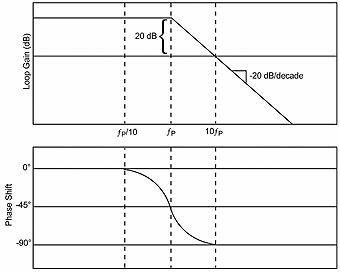

În acest punct, este momentul de a fi prezentată diagrama Bode, o unealtă simplă şi eficientă, foarte utilizată pentru analizarea stabilităţii buclelor închise. Diagrama Bode include graficul amplificării buclei şi graficul de defazare. Aceste grafice urmăresc deplasarea polilor şi zerourilor creaţi de impedanţele componentelor care formează bucla. Comportarea polilor şi zerourilor determină stabilitatea buclei.

Un pol scade panta caracteristicii de amplificare a buclei cu -20dB/decadă la frecvenţa sa, fP. El introduce de asemenea un defazaj de -90° (sens trigonometric) de la frecvenţa cu o decadă mai jos de fP (fP/10) la frecvenţa cu o decadă mai sus de fP (10fP), cu un defazaj de -45° la fP (Figura 2.a). Atât pantele caracteristicilor de amplificare, cât şi defazajele sunt aditive, în sensul că, fiecare pol adiţional scade panta amplificării cu încă -20dB/decadă, şi creşte defazajul cu încă -90°. O pereche RC într-un model de filtru trece jos determină un pol (Figura 2.b), cu fP definit ca:

fP = 1/2pRC, exprimată în Hz (2)

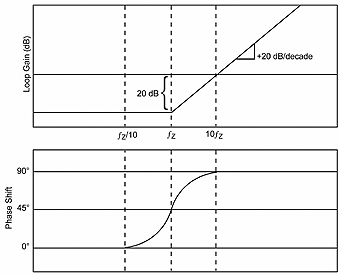

Un zero, pe de altă parte, creşte panta caracteristicii de amplificare a buclei cu +20dB/decadă la frecvenţa zeroului (fZ). El introduce de asemenea un defazaj de +90° (sens orar) de la frecvenţa cu o decadă mai jos de fZ (fZ/10) la frecvenţa cu o decadă mai sus de fZ (10fZ), cu un defazaj de +45° la fZ (Figura 3.a). Creşterea pantei amplificării buclei şi defazarea create de un zero sunt şi ele aditive. O pereche RC într-o configuraţie de filtru trece sus (Figura 3.b) determină un zero cu fZ definit de următoarea ecuaţie:

fZ = 1/2pRC, exprimată în Hz (3)

În exemplul dat (Figura 1.a), câştigul buclei închise (A) este dat ca:

A = 20log(|VA / VB|), exprimat în dB (4.a)

Cel mai important factor de indicare a stabilităţii unei bucle închise îl reprezintă limita de fază – phase margin (exprimată în grade), definită ca diferenţa dintre -180° şi defazarea totală a buclei la frecvenţa unde amplificarea buclei este de 0dB (amplificare unitară). Limita de fază este un număr pozitiv (sens orar) între 0° şi 180°, şi este exprimat ca:

F = 180° + defazaj (4.b)

* unde defazarea este un număr negativ (sens trigonometric) între 0° şi -180°

Pentru a menţine bucla stabilă, există o metodă empirică, ce spune că limita de fază nu trebuie să fie mai mică de 45° (Figura 1.b). Dacă limita de fază de 45° nu poate fi obţinută prin arhitectura internă a stabilizatorului liniar, este necesară aplicarea unor metode de compensare interne sau externe.

Se poate trece acum la analizarea stabilităţii stabilizatoarelor liniare. Fie pentru început un stabilizator standard NPN (Figura 4.a). Într-un astfel de stabilizator standard există doi poli – un pol dominant (PINT), creat de capacitatea internă a stabilizatorului şi un pol de putere (PPWR), creat de elementul de trecere. PINT şi PPWR apar la următoarele frecvenţe:

f(PINT) = 1/2pRINTCINT (5.a)

*unde RINT şi CINT sunt rezistenţa internă şi capacitatea internă a stabilizatorului

f(PPWR) = 1/2pRPWRCPWR (5.b)

*unde RPWR şi CPWR sunt rezistenţa şi capacitatea elementului de trecere

Deoarece perechea NPN Darlington se află în configuraţie colector comun, impedanţa sa de ieşire este foarte mică (i.e., RPWRCPWR este foarte mică). De aceea, PPWR apare la frecvenţe foarte mari (Ecuaţia 5.b). Dimpotrivă, PINT apare la frecvenţe joase datorită capacităţii relativ mari a stabilizatorului (Ecuaţia 5.a).

Totuşi, PPWR poate apare la o frecvenţă sub punctul de intersecţie de 0dB, ceea ce poate crea o limită de fază mai mică de 45°. Astfel, bucla poate deveni instabilă, ceea ce crează necesitatea unei compensări (Figura 4.b).

Stabilizatoarele standard NPN implică o schemă de compensare internă cunoscută sub numele de compensarea polului dominant (dominant pole compensation). Această compensare este realizată prin adăugarea unei capacităţi interne stabilizatorului.

Aceasta mută PINT la o frecvenţă mai mică (Ecuaţia 5.a) fără a afecta PPWR, făcând-o să apară la o frecvenţă peste punctul de intersecţie de 0dB. Limita de fază este în acest caz mai mare de 45°, generând astfel o buclă stabilă. În acest fel stabilizatoarele standard NPN sunt stabile fără compensare externă (Figura 4.b).

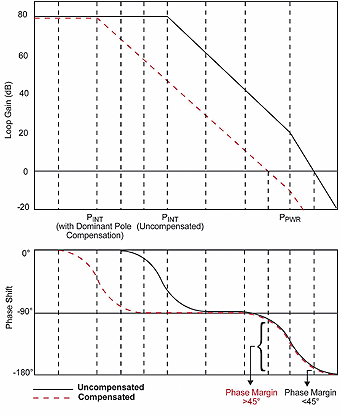

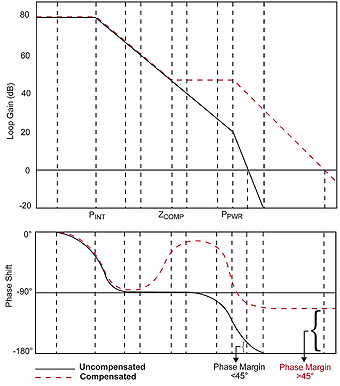

Stabilizatorul cu tranzistor de trecere NPN (Figura 5.a) are de asemenea un pol dominant (PINT) şi un pol de putere (PPWR). Ca şi stabilizatoarele standard NPN, cele cu tranzistor de trecere NPN sunt în configuraţie de colector comun cu impedanţă de ieşire mică. În această configuraţie, tranzistorul NPN este controlat de un tranzistor PNP cu impedanţă mare. Efectul net este că impedanţa sa de ieşire, deşi mare în raport cu alte tipuri de stabilizatoare liniare, nu este aşa de mare ca în cazul stabilizatorului standard NPN. De aceea, PPWR apare la o frecvenţă mai joasă decât la stabilizatoarele standard NPN, şi este uzual sub punctul de intersecţie de 0dB. Rezultatul este o limită de fază mai mică decât 45°, pentru care ar fi necesară compensare pentru menţinerea stabilă a buclei (Figura 5.b).

Din cauza frecvenţei relativ mici a PPWR, această configuraţie cu tranzistor de trecere NPN nu poate fi stabilizată doar prin compensarea polului dominant. În loc de aceasta va fi plasat un zero între PINT şi PPWR pentru a creşte limita de fază la cel puţin 45° (Figura 5.b). Operaţiunea este însoţită de utilizarea unei metode de compensare externe, precum adăugarea unui condensator pe ieşirea VOUT. Frecvenţa zeroului adăugat (ZCOMP) este definită de:

f(ZCOMP) = 1/(2p x ESR X COUT) (6)

*unde ESR este rezistenţa echivalentă serie a condensatorului de ieşire

Datorită faptului că PPWR încă apare la frecvenţe mari, selectarea condensatorului de ieşire este cât se poate de simplă. Atât timp cât f(ZCOMP) este mai mică decât f(PPWR), COUT poate fi mic, iar ESR nu este critic.

De QI Deng.senior Product Matketing Engineer

Microchip Tehnology Inc.

www.microchip.com

Continuare în numărul viitor