Dispozitivele LatticeXP2TM combină celule “Look-up Table” ( LUT) şi celulele nevolatile într-o arhitectură cunoscută sub denumirea de flexiFlash. Soluţia flexiFlash asigură o implementare single-chip cu beneficii cum ar fi operarea instant-on, stocarea on-chip folosind blocul Flash BAKTM embedded RAM backup, accesul la memoria Serial TAG de uz general.

Dispozitivele LatticeXP2 suportă reconfigurarea Live Update cu TransFRTM, 128 biţi AES bitstream encryption şi tehnologie Dual Boot.

Fabricaţia LatticeXP2 are la bază o arhitectură LatticeECP2TM optimizată de la început pentru a obţine cost redus şi performanţe ridicate. Dispozitivele Lattice XP2 suportă 4 intrări LUT, memorie embedded, Phased Locked Loops -PLLs, source synchronous I/O şi blocuri sysDSPTM numeroase.

Scula de proiectare ispLEVER® permite proiectelor complexe să fie eficient implementate folosind FPGA-urile familiei LatticeXP2. IspLEVER este complementat de modulele IP (Intellectual Property) ispLeverCORETM pentru LatticeXP2. Folosind aceste blocuri IP standardizate, proiectanţii sunt liberi să se concentreze asupra aspectelor unice ale proiectului lor crescându-le astfel productivitatea.

Elemente cheie şi beneficii

Arhitectura flexiFLASH

• instant-on (1 ms), integrare single chip

• tehnologie FlashBAKTM

• memorie de uz general Serial TAG

• securitatea proiectului

Tehnologia Live Update

• tehnologia TransFRTM – update-ul configuraţiei logice în timp ce echipamentul continuă să lucreze

• Dual Boot cu SPI Flash extern creşte siguranţa

• Update în siguranţă cu 128 biţi AES bitstream encryption

Arhitectura FPGA optimizată

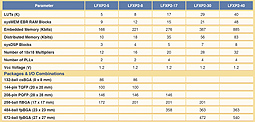

• Densităţi de la 5K la 40K 4 intrări LUTs

• Până la 885 Kbiţi blocuri RAM sysMEM

• Până la 83 Kbiţi RAM distribuit

• Capsule TQFP, PQFP şi BGA low cost

Blocuri înaltă performanţă sysDSPTM

• De la 3 la 8 blocuri cu multiply and accumulate

• De la 12 la 32 multiplicatoare 18×18

Bufferele flexibile sysIOTM suportă

– LVCMOS 3.3/2.5/1.8/1.5/1.2; LVTTL

– SSTL 18 clasa I,II; SSTL 3/2 clasa I,II

– HSTL15 clasa I;HSTL18 clasa I,II

– PCI

– LVDS, Bus-LVDS, LVPECL

Până la 4 sysCLOCKTM PLLs

Consumul în Standby redus cu 33%

System Level Support

• Interfaţă pentru programare SPI/JTAG

• IEE Standard 1149.1 Boundary Scan

• Oscilator onboard pentru iniţializare şi uz general

• Soft Error Detect logic

• Alimentare 1.2 V pentru nucleu

Scule proiectare ispLEVER®

IspLEVER®, softul de la Lattice,este un mediu de proiectare inteligent pentru arhitecturile LatticeXP2, sculă care include tot ceea ce aveţi nevoie pentru începerea proiectului, sinteză, simulare, managementul proiectului, programarea dispozitivelor şi multe altele.

Sculele de sinteză şi simulare de la liderii industriali Mentor Graphics şi Simplicity sunt incluse în softul ispLever .

IspLeverCORETM IP

Lattice oferă un portofoliu bogat de IP core pentru suportul integrării uşoare a celor mai des folosite funcţii , inclusiv :

– PCI Master/Target şi Target 64 biţi şi 32 biţi

– DDR/DDR2 controlere de memorie

– Compilator FFT

– Compilator FIR

– Microprocesor LatticeMico32

– Gigabit Ethernet MAC

– Viterbi Decoder OFDM

– Interleaver/De-interleaver

– Turbo Encoder/ Decoder

Plăci dezvoltare LatticeXP2

Lattice oferă spre alegere două plăci de dezvoltare pentru suportul proiectelor LatticeXP2.

Placa standard de evaluare Lattice XP2 şi placa de evaluare avansată LatticeXP2 oferă platforme de evaluare completă în laborator a beneficiilor şi facilităţilor dispozitivelor LatticeXP2.

Pentru detalii contactati:

ing. Marian Enache

mena@msc-ge.com

+40 21 230.2530

www.msc-ge.com

www.latticesemi.com