Motive pentru extinderea memoriei externe

Acolo unde este posibil, dezvoltatorii ar trebui să înceapă dezvoltarea aplicației prin selectarea unui microcontroler care are o foaie de parcurs cu dispozitive compatibile la nivel de pini cu mai multă memorie. Dacă în perioada dezvoltării, firmware-ul de aplicație se extinde până la depășirea memoriei Flash de pe dispozitivul țintă, un dispozitiv compatibil la nivel de pini, cu mai multă memorie Flash poate fi introdus cu ușurință. Acest lucru permite memoriei de aplicație să se extindă fără a trebui să se reproiecteze placa de circuit pentru diferite microcontrolere.

Totuși, aplicațiile pot necesita mai multă memorie de program decât este disponibilă pe cip pentru familia de microcontrolere compatibile la nivel de pini, necesitând astfel utilizarea unei memorii Flash în afara cipului. Acest lucru devine din ce în ce mai uzual și se poate datora unui număr de motive, inclusiv:

Figura 1: Adesto AT25SL321 este o memorie Flash de 32-Mbiți care suportă modurile SPI single, dual și quad. Dispune de 32-Mbiți de memorie Flash în capsule de 8 pini SOIC, DFN8 sau TSSOP8. — (Sursă imagine: Adesto Technologies)

• Scopul sistemului se poate extinde dincolo de conceptul său inițial, în perioada fazei de dezvoltare. Acest lucru se poate datora unor schimbări

de ultim moment în cadrul aplicației, variației unor caracteristici sau calculării imprecise a necesității de memorie a aplicației. Opțiunile sunt fie de a face upgrade cu un microcontroler compatibil la nivel de pini care să aibă mai multă memorie de program Flash fie să se adauge o memorie de program Flash suplimentară, lucru ce poate întârzia proiectul dacă dezvoltarea este deja avansată.

• Un viitor upgrade de firmware în teren poate necesita mai multă memorie de program Flash decât este disponibilă pe microcontrolerul aflat

deja pe placa de circuit. În această situație, opțiunile sunt limitate: fie înlocuirea sistemului în teren cu altul, conținând mai multă memorie de

program fie să se renunțe la upgrade.

• Dezvoltarea familiei de produse a sistemului poate necesita mai multă memorie de program Flash decât este deja disponibilă pentru familia de

microcontrolere compatibile la nivel de pini. Opțiunile sunt de a reproiecta sistemul utilizând

– nouă familie de microcontrolere sau să se adauge

– memorie de program Flash externă.

În mod clar, este important pentru dezvoltator să anticipeze și să planifice necesitatea de extensie a memoriei pentru sistemele prezente și viitoare. Dacă există posibilitatea ca proiectul să necesite o memorie de program Flash externă, dezvoltatorul trebuie să prevadă un loc pentru plasarea pe placă a extensiei viitoare. Chiar dacă cipul de memorie Flash nu are nevoie să fie plasat pe placă, este bine să se asigure un spațiu pentru acesta.

Calea tradițională de extensie a memoriei de program Flash a fost de utilizare a unei interfețe Flash paralele cu linii de date și adresă. Totuși, chiar și cea mai eficientă utilizare a memoriei Flash paralele care nu face sacrificii din punct de vedere a vitezei, poate utiliza 16 biți de adresă, 16 biți de date și patru sau mai multe semnale de control. Deci sunt necesari 36 sau mai mulți pini de la microcontroler.

Pe lângă faptul că este o utilizare ineficientă a resurselor microcontrolerului, acest lucru limitează selecția microcontrolerelor la dispozitive cu o magistrală externă, care crește numărul de pini ai microcontrolerului. O magistrală externă paralelă consumă, de asemenea, un spațiu pe placă semnificativ, în vreme ce magistrala de adrese și date de mare viteză crește posibilitatea de interferențe electromagnetice (EMI).

Executarea programului SPI XiP

O opțiune mai eficientă este utilizarea unui dispozitiv de memorie de program Flash externă care suportă o interfață SPI XiP. O astfel de interfață poate utiliza numai șase pini pentru interfațare la microcontrolerul gazdă. Spre deosebire de o interfață SPI convențională, memoria de pe dispozitivul de memorie externă Flash nu este direct accesată cu un driver firmware SPI, ci este mapată în memoria de program a microcontrolerului.

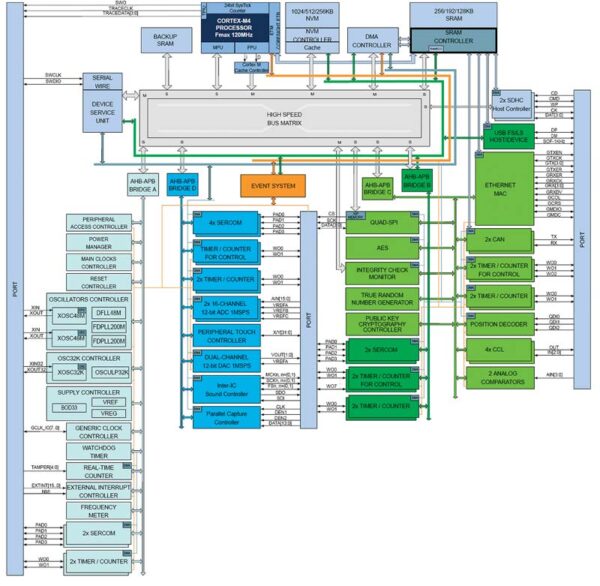

Figura 2: ATSAMD51J20A de la Microchip dispune de un set complet de periferice, incluzând interfață serială SPI XiP, ADC, DAC și suport pentru criptare de date. — (Sursă imagine: Microchip Technology)

Un bun exemplu de dispozitiv de memorie Flash serial proiectat pentru interfațare utilizând interfața SPI XiP este AT25SL321-UUE-T de la Adesto Technologies (Figura 1). Aceasta este o memorie Flash de 32-mega-biți (Mbiți) care suportă modurile SPI single, dual și quad. Aceasta suportă un ceas SPI de 104 MHz, ceea ce în modul SPI dual oferă o viteză de ceas echivalentă de 266 MHz, iar în modul SPI quad, o viteză de ceas echivalentă de 532 MHz. Pe lângă memoria Flash de 32-Mbiți, dispozitivul are regiștri de stare pentru a configura dispozitivul. Citirea de pe acești regiștri poate spune firmware-ului dacă dispozitivul are în progres o operație de scriere sau citire. Scrierea în regiștrii de stare permite ca blocuri de memorie Flash să fie protejate la scriere.

Adesto AT25SL321 are, de asemenea, 4-kilo-biți (Kbiți) de memorie programabilă o singură dată (OTP), care poate fi utilizată pentru a stoca informații de securitate precum un număr serial unic. Dispozitivul este disponibil în capsulă cu 8-pini SOIC, DFN8 sau TSSOP8.

Ca toate dispozitivele de memorie seriale care suportă SPI XiP, Adesto AT25SL321 este configurat utilizând un set de instrucțiuni specific dispozitivelor Adesto. Setul de instrucțiuni constă din 38 de comenzi care sunt utilizate de microcontrolerul gazdă pentru a controla memoria Flash serială.

Perifericul SPI XiP pe un microcontroler gazdă va include o mașină de stare programabilă care este inițializată la pornirea microcontrolerului cu setul de instrucțiuni al memoriei Flash seriale țintă. Odată inițializată, operarea perifericului SPI este transparentă programului de executare a firmware-ului în regiunea de memorie mapată a SPI XiP.

De exemplu, dacă firmware-ul microcontrolerului gazdă citește datele din regiunea mapată de memorie, SPI XiP, care este configurată cu setul de instrucțiuni Adesto, trimite un cod de instrucțiune Read Data (date citite) urmat de o adresă de 24-biți către memoria serială Adesto. Aceasta trimite apoi conținutul memoriei către microcontrolerul gazdă, câte un byte odată. Pentru firmware, acest lucru apare ca o citire normală de memorie.

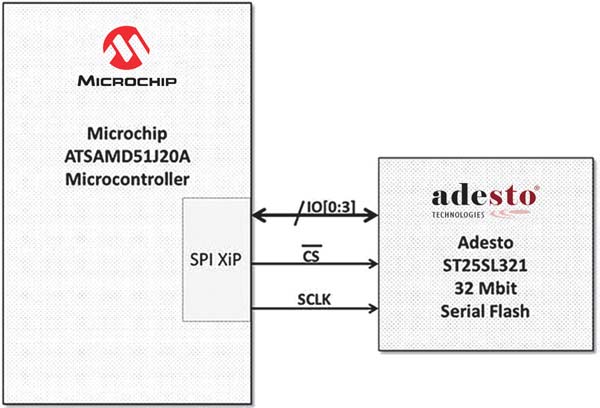

Figura 3: Microcontrolerul pe 32-biți ATSAMD51J20A de la Microchip are un periferic QSPI care suportă un port serial SPI XiP. Acesta se poate interfața cu ușurință la memoria Flash serială Adesto AT25SL321, utilizând numai șase pini. — (Sursă imagine: Digi-Key Electronics)

Pe lângă un ceas SPI, pini de date și selecție cip, Adesto AT25SL321 are doi pini suplimentari pentru funcționalitate îmbunătățită în sistem. WP este un pin de protecție la scriere de tip activ în stare inferioară (active-low) care previne scrierea de blocuri de cod în registrul de stare. Microcontrolerul poate utiliza acest pin pentru a preveni ca sarcinile de joasă prioritate să facă schimbări neautorizate. HOLD este utilizat pentru face o pauză în transferul de date aflat în progres. Acest lucru poate fi util dacă microcontrolerul recepționează un semnal de întrerupere de prioritate ridicată în momentul unui transfer de date către memorie și este nevoie de o pauză până când se răspunde întreruperii.

Dispozitivul Flash Adesto AT25SL321 pe 32-Mbiți suportă patru moduri de operare:

• Operare SPI standard: memoria Flash este accesată precum un dispozitiv de memorie SPI standard cu ceas SPI (SCLK), selecție cip de tip activ

pe nivel inferior (CS), date de intrare seriale (SI) și date de ieșire seriale (SO). Sunt suportate modurile de magistrală SPI standard 0 și 3.

• Operare SPI duală: aceasta oferă o viteză dublă față de operarea SPI standard, prin utilizarea SI și SO ca pini de date bidirecționali, proiectați ca

IO0 și IO1.

• Operare SPI Quad: aceasta oferă o viteză de transfer de patru ori mai mare față de operarea SPI standard. Pe lângă IO0 și IO1, sunt utilizați ca

pini de date bidirecționali și WP și HOLD, IO2 și IO3. Evident că, în operarea SPI quad, funcțiile WP și HOLD nu sunt disponibile.

• Operarea QPI: aceasta este utilizată numai pentru operarea SPI XiP. În vreme ce modurile SPI standard, dual și quad suportă trimiterea de

comenzi memoriei SPI utilizând numai pinul IO0, operarea QPI suportă trimiterea comenzilor utilizând cei 4 pini IO[0:3], îmbunătățind semnificativ performanțele SPI XiP.

Dacă cei 32-Mbiți ai Adesto AT25SL321 nu sunt suficienți, Adesto oferă, de asemenea, AT25QL641-UUE-T de 64-Mbiți. Cele două dispozitive sunt compatibile la nivel de pini, astfel încât AT25QL641 poate fi un înlocuitor. Pe lângă faptul că are mai multă memorie, singura diferență între cele două dispozitive este aceea că AT25QL641 intră implicit în modul de operare QPI, la alimentare. Acest lucru reduce timpul de pornire a dispozitivului în sistemele de înaltă performanță. Ambele dispozitive consumă numai 5 mA pe un ciclu de citire a memoriei. Ambele dispozitive de memorie Adesto operează de la o singură linie de la 1.7 la 2V și se poate interfața cu orice microcontroler compatibil ca tensiune, care are o interfață SPI XiP.

Pentru microcontrolerul gazdă, Microchip Technology oferă interfețe SPI XiP pe seria sa ATSAMD51, inclusiv pe microcontrolerul său ATSAMD51J20A-UUT de 120 MHz bazat pe Arm®Cortex®-M4F. Acest dispozitiv are o memorie Flash de 1-Mbyte și 256-Kbyte de memorie RAM. El are o gamă completă de periferice, inclusiv un convertor analog-digital (ADC), convertor digital-analog (DAC), port USB și I2S. De asemenea, acesta dispune de un periferic de criptare cu chei publice și un generator real de numere aleatoare (TRNG – True Random Number Generator) pentru funcții de securitate.

Pentru conectare la memoria Flash externă, dezvoltatorii pot utiliza perifericul QSPI al ATSAMD51J20A care suportă SPI XiP. Acesta permite programului să fie executat direct din memoria Flash Adesto. ATSAMD51J20A mapează memoria Flash Adesto în spațiul memoriei de program AHB (Advanced High-Performance Bus) de la Arm. Pentru a proteja datele din memoria Flash serială, ATSAMD51J20A SIP XiP suportă o amestecare transparentă a datelor scrise în memoria externă SPI și apoi rearanjarea datelor citite din memoria SPI externă. Acest lucru previne copierea neautorizată a firmware-ului și piratarea sistemului.

Utilizarea ATSAMD51J20A de la Microchip cu un dispozitiv de memorie serială flash

Perifericul ATSAMD51J20A SPI XiP de la Microchip, are trei regiștri utilizați pentru a trimite comenzi către o memorie Flash serială XiP. Deoarece dispozitivele de memorie serială Flash XiP de la diferiți furnizori utilizează diferite coduri de instrucțiuni, acești regiștri trebuie să fie configurați de către dezvoltatori după cum urmează, în funcție de furnizorul de memorie:

1. Instruction Code Register conține instrucțiunea utilizată pentru a accesa memoria serială Flash. Pentru un dispozitiv de memorie Flash Adesto

operând în modul SPI quad, acest registru conține instrucțiunea de citire rapidă a ieșirii Quad (Fast Read Quad Output) 0x6B dacă firmware-ul

execută programul în afara memoriei mapate în regiunea XiP. Conținutul acestui registru trebuie să fie schimbat cu codul potrivit de instrucțiune

dacă se dorește realizarea unor operații de scriere, ștergere sau stare.

2. Instruction Address Register conține adresa care este accesată din memoria externă Flash. Atunci când ATSAMD51J20A SPI XiP de la

Microchip este configurat pentru modul de memorie serială, această adresă este alocată automat de perifericul SPI XiP adresei care este

executată de firmware în spațiul de memorie mapat AHB în plaja 0x0400 0000 – 0x0500 0000.

3. Instruction Frame Register configurează SPI XiP pentru formatul de instrucțiune specific dispozitivului de memorie externă utilizat. Acesta include selectarea lungimii adresei de 24 sau 32-biți, permițând o viteză de transfer de date dublă (DDR), dacă sunt suportate modul de citire

continuă și lungimea codului de operare.

Restul interfeței Microchip SPI XiP se configurează ușor utilizând driverele SPI Microchip.

Atât timp cât firmware-ul de aplicație de pe microcontroler execută un program în afara regiunii mapate a memoriei SPI XiP, perifericul SPI XiP de pe microcontroler nu trebuie să fie reconfigurat.

Memoria Flash Adesto suportă, de asemenea, un mod de citire cu numai un singur pin SI cu codul de instrucțiune 0x03. Dacă este utilizat numai modul dual SPI, codul de instrucțiune este 0x3B. Aceste coduri sunt scrise de firmware-ul de aplicație în registrul cod de instrucțiuni.

Este considerată o bună practică să se șteargă toate cache-urile asociate cu spațiul de adresă al memoriei mapate, atunci când conținutul registrului de cod de instrucțiuni este schimbat. Când se scrie sau se citește de pe regiștrii de stare ai memoriei Flash seriale, cache-ul trebuie șters, apoi dezactivat. Acest lucru trebuie, de asemenea, făcut la scrierea în Flash în regiunile de memorie mapată. Cache-ul ar trebui să fie reactivat odată ce sunt reluate operațiile de citire a memoriei.

Datorită transferului de date de mare viteză implicat, memoria Flash serială trebuie să fie plasată pe placa de circuit imprimat cât mai aproape posibil de portul SPI XiP al microcontrolerului. Dacă acest lucru nu este posibil, atunci niciun traseu nu ar trebui să fie mai lung de 120 milimetri (mm). Pentru a evita interferențele, semnalul de ceas ar trebui să aibă lățimea traseului pe placa de circuit de 3 ori mai mare decât celelalte semnale. Semnalele de date bidirecționale IO[0:3] ar trebui să fie toate în limita a 10mm unul de celălalt pentru a evita distorsiunile.

Concluzie

Dispozitivele de memorie Flash serială externe pot oferi o execuție rapidă a programului firmware fără complexitatea și excesul de spațiu pe placă al cipurilor paralele. Aceasta permite extensia în timp a programului cu ușurință, precum și actualizări în teren fără reproiectarea plăcii sistemului.

Autor: Rich Miron – Inginer de aplicații

Autor: Rich Miron – Inginer de aplicații

Rich Miron, Inginer de aplicații la Digi-Key Electronics, face parte din grupul de autori care crează articole tehnice (Technical Content Group) din 2007, având responsabilitatea principală de a scrie și edita articole, bloguri și module de instruire pentru cunoașterea produselor.

Înainte de Digi-Key, el a testat și calificat sisteme de control și instrumentare pentru submarine nucleare. Rich deține o diplomă în inginerie electrică și electronică de la Universitatea de Stat din North Dakota din Fargo, ND.

Digi-Key Electronics | https://www.digikey.com