Acest articol analizează principalele criterii de proiectare care trebuie luate în considerare la alegerea unui FPGA destinat aplicațiilor cu resurse limitate. Sunt prezentate și exemple relevante din portofoliul Altera de dispozitive FPGA optimizate pentru consum redus și eficiență economică. În încheiere, sunt evidențiate kiturile de dezvoltare și plăcile de evaluare disponibile pentru prototiparea și validarea conceptelor de proiectare.

În sistemele embedded cu resurse limitate, cererea pentru logică configurabilă este în continuă creștere. Aplicații avansate precum inteligența artificială (AI), viziunea artificială și automatizările industriale au nevoie de o logică flexibilă, adaptată fiecărui caz de utilizare, pentru a răspunde cerințelor ridicate de performanță, respectând totodată constrângerile stricte legate de consumul de energie, dimensiune și costuri. Matricile logice programabile (FPGA) de ultimă generație pot satisface aceste cerințe simultan.

Considerații privind alegerea unui FPGA

Alegerea unui FPGA pentru un sistem cu resurse limitate presupune corelarea cerințelor de proiectare cu caracteristicile dispozitivelor disponibile. Există mai mulți factori esențiali care trebuie luați în calcul:

Capacitatea elementelor logice (LE – Logic Element)

Elementele logice reprezintă unitățile fundamentale ale unui FPGA. Numărul acestora determină câtă logică personalizată poate fi implementată. Un număr mai mare permite proiectarea unor sisteme mai complexe, însă vine la pachet cu un consum mai ridicat de energie, costuri mai mari și capsule de dimensiuni mai mari.

I/O și memorie

FPGA-urile sunt adesea utilizate pentru a integra componente disparate într-un sistem, ceea ce face ca numărul de pini de intrare/ieșire să fie un parametru esențial. Pentru a îmbunătăți performanța I/O, multe FPGA-uri includ blocuri logice fixe pentru interfețe precum PCI Express (PCIe), memorie de mare viteză și transceivere multi-gigabit.

Unele dispozitive integrează funcții suplimentare precum convertoare analog-digitale (ADC) sau memorie Flash, ceea ce poate reduce nevoia de componente externe, economisind spațiu pe placă și sporind eficiența energetică.

Integrarea procesorului

În locul unui procesor extern, un microprocesor (MPU) “soft” poate fi implementat direct în FPGA. Această soluție este ideală pentru aplicații cu cerințe reduse de procesare. Pentru sarcini mai solicitante, se poate opta pentru un FPGA cu procesor “hard” (HPS – Hard Processor System), unde microprocesorul este integrat sub formă de bloc logic dedicat.

Acceleratoare hardware

FPGA-urile includ, de obicei, blocuri dedicate de procesare a semnalelor digitale (DSP), care gestionează eficient sarcini solicitante din punct de vedere computațional, cum ar fi controlul mișcării. Dispozitivele de ultimă generație pot integra și unități (sau blocuri) pentru operații tensoriale, specializate în sarcini de inteligență artificială (AI). Capabilitățile acestor blocuri de accelerare variază semnificativ între familiile de FPGA-uri și pot influența considerabil performanța generală a sistemului.

Optimizări pentru capsulă și consum energetic

Unele FPGA-uri sunt proiectate special pentru a avea o amprentă fizică și electrică redusă, oferind, de exemplu, moduri “sleep” cu consum ultra-redus, utile în aplicațiile alimentate din baterie.

Instrumente de dezvoltare

Proiectarea logicii personalizate poate fi o sarcină dificilă, mai ales pentru cei care nu au experiență anterioară. Platforme precum Quartus Prime de la Altera au fost create pentru a simplifica acest proces. Ele oferă o interfață prietenoasă, o bibliotecă extinsă de blocuri predefinite și opțiuni automate de interconectare.

În plus, Quartus Prime este compatibil cu fluxurile de lucru moderne din domeniul AI și machine learning (ML), permițând dezvoltarea de aplicații bazate pe sisteme de operare cunoscute, cum ar fi Linux și Zephyr.

Aceste capabilități pot accelera semnificativ procesul de dezvoltare, motiv pentru care instrumentele software disponibile reprezintă un criteriu esențial în alegerea unui FPGA.

Calcul de înaltă performanță pentru sarcini de lucru embedded avansate

Pentru a ilustra modul în care cerințele de proiectare influențează selecția unui FPGA, este util să analizăm aplicații de ultimă generație care necesită o densitate ridicată de calcul, o lățime de bandă extinsă și un nivel ridicat de integrare. Exemple relevante includ aplicații AI avansate și gateway-uri industriale de înaltă performanță.

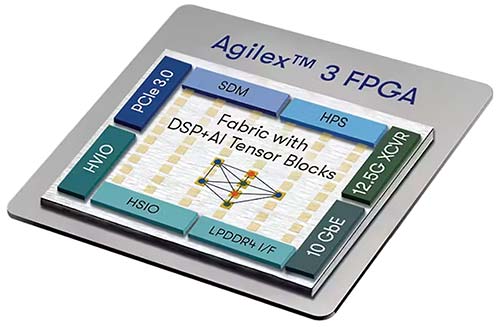

FPGA-urile Agilex 3 (Figura 1) sunt proiectate pentru a răspunde acestor cerințe, oferind până la 135.000 de elemente logice (LE). Cipurile sunt disponibile atât în versiuni FPGA clasice, cât și ca SoC-uri (sisteme pe cip). Acestea din urmă integrează un procesor dual-core Arm® Cortex®-A55, tactat la 800 megahertzi (MHz), care permite gestionarea unor stive software complexe, precum interfețele om-mașină (HMI) sau stivele de rețea.

Structura programabilă include unități pentru operații tensoriale (AI Tensor Blocks) capabile să atingă până la 2,8 tera operații pe secundă (TOPS) pentru calcule în format INT8. Aceste blocuri suportă și alte tipuri de precizie – precum FP16, FP19, FP32 și BFLOAT16 – și sunt optimizate pentru execuția eficientă a sarcinilor AI. În plus, sunt incluse blocuri DSP cu precizie variabilă, care oferă până la 180 giga operații în virgulă mobilă pe secundă (GFLOPS) pentru procesarea generală a semnalelor.

Figura 1: FPGA-ul Agilex 3 se remarcă prin blocurile DSP și unitățile AI specializate pentru operații tensoriale. (Sursa imaginii: Altera)

Conectivitatea de mare viteză este un alt punct forte al arhitecturii Agilex 3. Transceiverele acceptă viteze de transfer de până la 12,5 gigabiți pe secundă (Gbps), iar blocurile I/O integrate suportă interfețe precum PCIe 3.0, 10 Gigabit Ethernet (10 GbE) și LPDDR4. În plus, suportul pentru sincronizare temporală precisă, conform standardului IEEE 1588, îmbunătățește compatibilitatea cu rețelele industriale în timp real.

Dispozitivul A3CZ135BB18AE7S ilustrează bine capabilitățile acestei familii: oferă 135.000 LE, 184 blocuri DSP și o performanță AI de 2,54 TOPS.

Integrare avansată pentru sisteme complexe

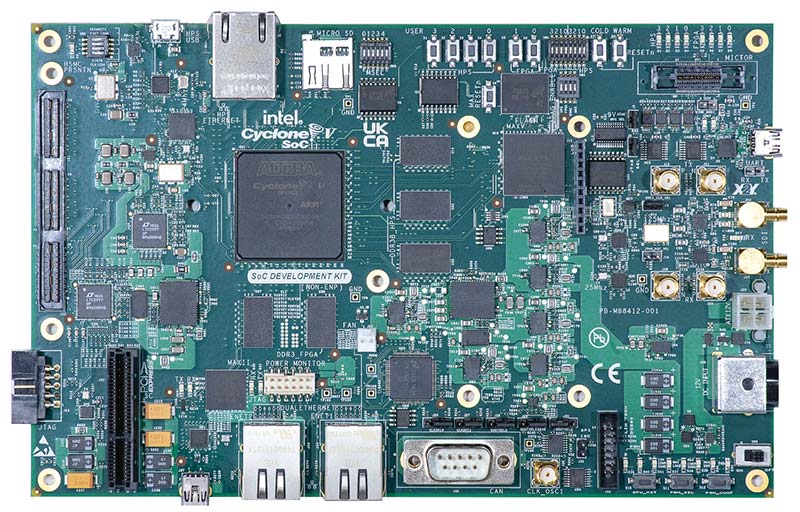

Pentru aplicații precum automatizările industriale și sistemele de viziune de nivel mediu, puterea brută de calcul poate fi mai puțin importantă decât capacitatea de a gestiona configurații complexe, cu volume mari de logică personalizată și interfețe I/O variate. FPGA-urile din seria Cyclone V sunt potrivite pentru astfel de scenarii, oferind până la 300.000 de elemente logice (LE) și interfețe de mare viteză extinse. La fel ca seria Agilex 3, aceste cipuri sunt disponibile atât în versiuni FPGA independente, cât și în variante SoC (System on Chip). În acest caz, dispozitivele SoC integrează un procesor dual-core Arm® Cortex®-A9.

Figura 2: Kitul de dezvoltare DK-DEV-5CSXC6N-B Cyclone V permite prototiparea de înaltă performanță. (Sursa imaginii: Altera)

Structura programabilă a acestor cipuri include blocuri DSP cu precizie variabilă, care acceptă operații precum triplă multiplicare în virgulă fixă 9 × 9, dublă 18 × 18 și multiplicare 27 × 27 în virgulă fixă sau mobilă. Aceste blocuri sunt ideale pentru procesarea avansată a semnalelor și sarcini AI.

Cipurile oferă o gama variată de opțiuni I/O, suportând multiple niveluri de tensiune și tipuri de interfețe. Blocurile logice dedicate permit conectivitate de mare viteză, inclusiv PCIe 2.0, controlere DDR3 și transceivere capabile de viteze de până la 6,144 Gbit/s.

Dezvoltatorii pot evalua familia Cyclone V SoC cu ajutorul kitului de dezvoltare DK-DEV-5CSXC6N-B (Figura 2). Acest kit este conceput pentru prototiparea rapidă a sistemelor embedded complexe, cu cerințe ridicate de performanță.

Kitul include funcții esențiale precum:

- Două porturi Ethernet, un conector PCIe x4 și o placă mezanin de mare viteză (HSMC – High Speed Mezzanine Card) cu 16 canale LVDS în fiecare direcție

- USB 2.0 OTG, CAN, UART și o interfață LCD cu text pe două linii

- 1 Gigabyte (Gbyte) DDR3 SDRAM pentru fiecare dintre componentele FPGA și HPS, 128 Megabytes (Mbytes) de memorie Flash SPI în configurație quad, și un card microSD de 4 Gbyte.

Placa include dispozitivul 5CSXFC5D6F31C8N, echipat cu procesor dual-core Arm Cortex-A9 cu frecvență de 600 MHz, 85.000 LE, 87 blocuri DSP și 288 pini I/O, într-o capsulă 896-FBGA de 31 mm × 31 mm.

Logică configurabilă cu consum redus de energie într-un format compact

Multe aplicații embedded se confruntă cu constrângeri stricte de spațiu și consum energetic. Exemple relevante includ interfețele pentru senzori, secvențierea alimentării și controlul perifericelor. FPGA-urile din familia MAX 10, oferă o soluție eficientă pentru aceste scenarii. Dispozitivele sunt disponibile în configurații de la 2.000 până la 50.000 de elemente logice (LE) și în capsule de dimensiuni reduse, începând de la 3 mm × 3 mm.

Printre caracteristicile cheie se numără:

- Până la două convertoare analog-digitale (ADC) pe 12 biți,

- Interfață de memorie DDR3,

- Blocuri multiplicatoare dedicate, care acceptă operații în virgulă fixă de tip 18 × 18 și dual 9 × 9.

Memoria Flash integrată, cu suport pentru stocare duală a imaginilor de configurare, permite autoconfigurarea dispozitivului fără a necesita o memorie externă.

Funcții de economisire a energiei

Funcțiile de economisire a energiei sunt printre cele mai remarcabile caracteristici ale familiei MAX 10. Un mod “sleep” integrat poate reduce consumul dinamic cu până la 95%. Iar datorită memoriei Flash interne, dispozitivele pot fi complet oprite și repornite în mai puțin de 10 milisecunde (ms).

Folosirea unei singure surse de putere simplifică arhitectura de alimentare, recomandând MAX 10 pentru aplicații de supraveghere cu secvențe de pornire care necesită activarea prioritară a unor zone de alimentare.

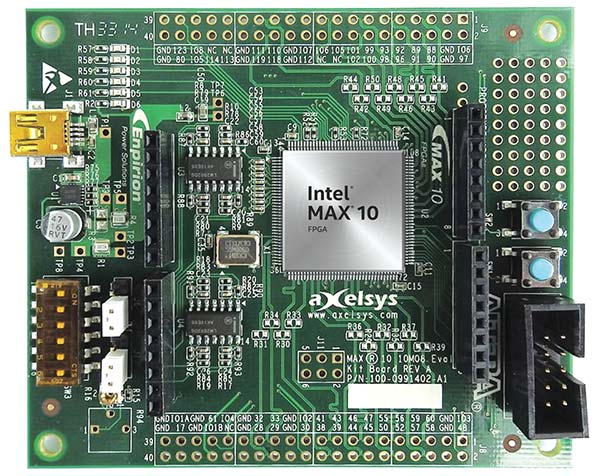

Pentru evaluarea rapidă a acestei familii, dezvoltatorii pot utiliza placa de evaluare MAX 10 FPGA EK-10M08E144 (Figura 3). Aceasta oferă acces facil la semnale externe prin conectori compatibili cu Arduino UNO R3 și puncte de testare, într-un layout gândit special pentru analiza performanței ADC-ului și a comportamentului energetic general.

Figura 3: Placa de evaluare MAX 10 FPGA EK-10M08E144 oferă acces facil la intrările/ieșirile principale. (Sursa imaginii: Altera)

Placa include dispozitivul 10M08SAE144C8G, care oferă 8.000 LE și un ADC, fiind integrat într-o capsulă LQFP cu 144 de pini. Pe lângă resursele hardware încorporate, acest FPGA este compatibil cu procesorul soft Nios® V, bazat pe arhitectura RISC-V, permițând proiectanților să implementeze funcții de control simple fără a recurge la un microcontroler (MCU) extern.

Performanță echilibrată pentru aplicații de nivel mediu

Unele aplicații embedded necesită mai multă logică și mai multe interfețe I/O decât pot oferi FPGA-urile din gama entry-level. Exemple relevante includ fuziunea datelor de la senzori, controlul mișcării și interconectările chip-to-chip – adică legături directe de date între circuite integrate, fără procesare intermediară. FPGA-urile Cyclone 10 LP sunt potrivite pentru aceste cerințe, oferind până la 120.000 de elemente logice (LE) și 525 de pini I/O, în dispozitive optimizate pentru un echilibru între consumul de energie, lățimea de bandă și cost.

Similar cu familia MAX 10, aceste dispozitive includ blocuri DSP potrivite pentru aplicații precum filtrarea semnalelor, bucle de control și sarcini simple de inferență AI. Spre deosebire de MAX 10, Cyclone 10 LP integrează transceivere LVDS dedicate, esențiale pentru comunicații de mare viteză, și terminare internă (OCT – On-Chip Termination), eliminând necesitatea unor rezistențe externe și simplificând astfel designul PCB-ului.

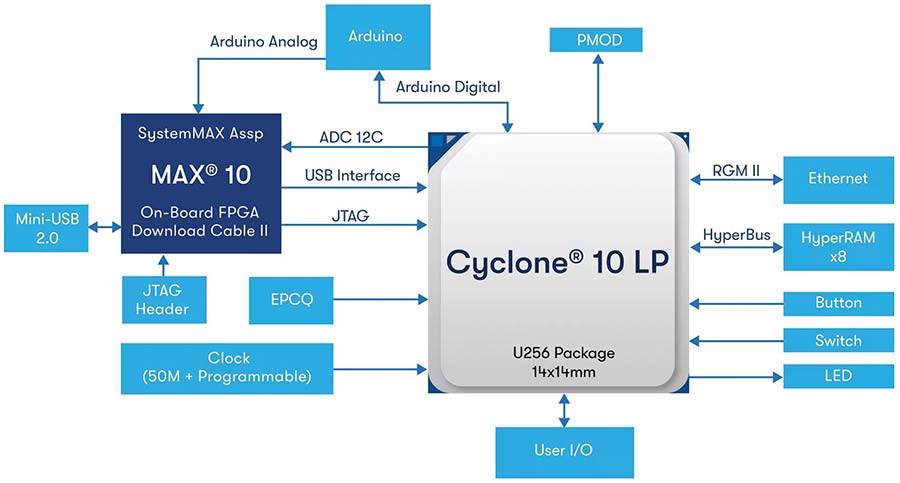

Figura 4: Kitul de evaluare EK-10CL025U256 Cyclone 10 permite extinderea facilă a perifericelor. (Sursa imaginii: Altera)

Pentru evaluare, dezvoltatorii pot utiliza kitul EK-10CL025U256 Cyclone 10 (Figura 4), care oferă conectori Arduino UNO R3 și Digilent Pmod pentru extindere rapidă. Alte caracteristici includ Ethernet Gigabit (GbE), USB 2.0, 128 Mbiți de SDRAM și 64 Mbiți de memorie Flash.

Placa este echipată cu dispozitivul 10CL025YU256C8G, care oferă 25.000 LE, 66 blocuri DSP și 150 pini I/O, într-o capsulă compactă de 14 mm × 14 mm. La fel ca familia MAX 10, Cyclone 10 LP suportă și procesorul soft Nios® V (bazat pe arhitectura RISC-V).

Concluzie

Proiectanții beneficiază astăzi de o flexibilitate mai mare în implementarea logicii personalizate în sisteme embedded. Aplicațiile de înaltă performanță pot profita de FPGA-uri cu acceleratoare AI integrate, în timp ce sistemele cu consum redus de energie pot utiliza dispozitive cu moduri “sleep” foarte eficiente. Pentru proiecte care necesită conectivitate extinsă, sunt disponibile FPGA-uri cu un număr mare de pini și interfețe de mare viteză.

Important este că toate aceste capabilități pot fi realizate în cadrul unor sisteme embedded cu resurse limitate, utilizând kituri de dezvoltare accesibile și intuitive pentru prototipare și validare.

Autor: Rolf Horn – Inginer de aplicații

Autor: Rolf Horn – Inginer de aplicații

Rolf Horn, inginer de aplicații la DigiKey, face parte din grupul european de asistență tehnică din 2014, având responsabilitatea principală de a răspunde la orice întrebări legate de dezvoltare și inginerie de la clienții finali din EMEA, precum și de a scrie și corecta articole și bloguri în limba germană pe platformele TechForum și maker.io ale DK. Înainte de DigiKey, a lucrat la mai mulți producători din domeniul semiconductorilor, axându-se pe sisteme embedded FPGA, microcontrolere și procesoare pentru aplicații industriale și auto. Rolf deține o diplomă în inginerie electrică și electronică de la Universitatea de Științe Aplicate din München, Bavaria și și-a început cariera profesională la un distribuitor local de produse electronice în calitate de arhitect de soluții de sistem pentru a-și împărtăși cunoștințele și expertiza în continuă creștere în calitate de consilier de încredere. Hobby-uri: petrecerea timpului cu familia + prietenii, călătoriile cu autorulota personală VW-California și plimbarea cu motocicleta, un BMW GS 100 din 1988.

DigiKey | https://www.digikey.ro

![]()

Glosar de termeni

| FPGA (Field-Programmable Gate Array) | Circuit integrat configurabil după fabricație, utilizat pentru implementarea de logică digitală personalizată. |

| LE (Logic Element) | Element logic fundamental într-un FPGA, utilizat pentru construirea circuitelor digitale personalizate. |

| HPS (Hard Processor System) | Microprocesor implementat ca bloc hardware fix în interiorul unui FPGA. |

| DSP (Digital Signal Processing) | Blocuri specializate pentru procesarea eficientă a semnalelor digitale. |

| Unități pentru operații tensoriale | Blocuri hardware dedicate operațiilor matematice de tip tensorial, folosite în AI și ML. |

| TOPS (Tera Operations Per Second) | Măsură a performanței AI – număr de operații INT8 pe secundă în ordinul tera. |

| GFLOPS (Giga Floating Point Operations Per Second) | Măsură a performanței pentru operații în virgulă mobilă. |

| ADC (Analog to Digital Converter) | Convertor analog-digital – transformă semnale analogice în valori digitale. |

| RISC-V | Arhitectură deschisă de set de instrucțiuni (ISA), pe baza căreia este construit procesorul soft Nios® V. |

| Nios® V | Procesor soft dezvoltat de Intel/Altera, bazat pe arhitectura RISC-V și implementabil pe FPGA. |

| LVDS (Low Voltage Differential Signaling) | Tehnologie pentru transmiterea de date la viteză mare cu consum redus de putere. |

| OCT (On-Chip Termination) | Tehnologie prin care rezistențele de terminare sunt integrate direct în cip pentru semnale I/O de mare viteză. |

| DDR3 / LPDDR4 / SPI Flash | Tipuri de memorii cu interfețe diferite pentru stocare sau transfer rapid de date. |

| PCIe (Peripheral Component Interconnect Express) | Interfață de mare viteză pentru conectarea dispozitivelor periferice. |

| GbE (Gigabit Ethernet) | Rețea Ethernet cu o viteză de transfer de 1 Gbit/s. |

| IEEE 1588 | Standard pentru sincronizarea precisă a timpului în rețele distribuite. |

| HSMC (High Speed Mezzanine Card) | Conector standard pentru extensii rapide pe plăcile FPGA. |

| UNO R3 / Digilent Pmod | Formate standard de conectori pentru extensii hardware compatibile cu platforme embedded. |