Actel a anunţat recent lansarea CoreMP7 – primul miez soft ARM optimizat pentru utilizare în FPGA – ca răspuns la tendinţele din industrie. Cele mai importante tendinţe sunt: trecerea de la ASIC la FPGA pentru toate proiectele de SoC (system-on-chip) şi creşterea utilizării proceselor pe 32 de biţi în aplicaţii în care iniţial se utilizau microcontrolere simple pe 8 biţi.

Deşi există pe piaţă şi alte soluţii de procesoare soft IP pentru implementare în FPGA, nici una nu are soliditatea pe piaţă furnizată de ARM. Aceasta se poate evidenţia în sectoarele auto, de bunuri de larg consum şi industrial. În aceste cazuri, ARM este atât de utilizat încât a devenit un standard: dispune de o imensă bază de programe cod, precum şi un bogat sistem de unelte, suport tehnic şi informaţii de proiectare.

CoreMP7, versiunea optimizată ARM7 a Actel este disponibilă pentru utilizare cu familia de dispozitive M7 ProASIC3/E, ce are la bază tehnologia flash nevolatilă a companiei, suportând de la 250k la 3M porţi în sistem şi până la 616 I/O de înaltă performanţă. De remarcat este faptul că utilizatorul final nu trebuie să plătească taxe de licenţiere, el cumpărând efectiv miezul împreună cu componenta.

Caracteristicile de bază ale dispozitivelor Actel M7 ProASIC3 sunt ideale pentru aplicaţii embedded bazate pe miez: în primul rând sunt sigure şi dispun de componente cu consum energetic redus. Ele sunt reprogramabile şi oferă timp redus de lansare pe piaţă la un cost de dispozitiv ASIC, dispunând în acelaşi timp memorie on-chip şi circuite de condiţionare temporală bazate pe până la 6 PLL (phase-locked loops) încorporate.

Mai mult, arhitectura ProASIC3 este dorită în multe aplicaţii de piaţă în care ARM impune procesarea pe 32 de biţi. În particular, dispozitivele oferă o combinaţie excepţională între preţ, performanţă, densitate şi caracteristici pentru utilizare pe piaţă, unde: 80% din proiecte necesită un milion de porţi sistem sau mai puţine, 75% din proiecte rulează la mai puţin de 140MHz, şi aproape toate sistemele au memorie de 512Kbit sau mai puţin. Gartner Dataquest a prezis o creştere de aproape 10 ori a utilizării FPGA în aplicaţii electrocasnice pentru perioada 2002 – 2008. Ca şi în cazul sectorului auto, preţurile cheie pentru asemenea aplicaţii sunt: sub-$2, sub-$5, sub-$10 şi sub-$20.

Caracteristicile de securitate ale ProASIC3 reprezintă un element important al relaţiei dintre ARM şi Actel, deoarece miezul este implementat chiar în FPGA: ARM este prin tradiţie circumspect în permiterea unei astfel de implementări soft, cauzat de posibilitatea ca utilizatorii să se amestece – sau chiar să fure – proprietatea sa intelectuală. Dispozitivele M7, având la bază memorie flash, sunt rezistente la modificări neautorizate, putând folosi tehnologia patentată FlashLock şi motorul de criptare AES al dispozitivului, asigurând că datele de configurare nu pot fi decodate sau utilizate cu alte dispozitive decât cu cele pentru care au fost concepute.

În timp ce această strategie oferă securitate IP-ului ARM, la fel de important este faptul că permite utilizatorului final să beneficieze de toată flexibilitatea asociată cu abordarea FPGA. Utilizatorii pot adăuga şi conecta în siguranţă propriul IP la procesor; toate IP-urile pot fi şterse şi reprogramate, beneficiind de aceeaşi siguranţă.

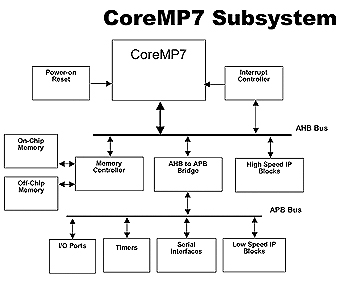

Designul miezului este o versiune a ARM7TDMI-S optimizată pentru viteză şi dimensiuni necesare implementării în structura Actel FPGA. El implementează arhitectura pe 32/16-biţi a ARMv4T (32-biţi ARM şi 16-biţi set de instrucţiuni). Procesorul are 3 nivele de pipeline, ALU pe 32-biţi, registre pe 32-biţi, adresă externă pe 32-biţi, interfaţă de date şi interfaţă JTAG de depanare.

Setul de caracteristici este realizat nu numai pentru a permite proiectanţilor implementarea unor arhitecturi similare ASIC cu avantajele de cost structură şi timp de lansare pe piaţă ale FPGA, ci şi pentru a furniza avantaje într-o integrare ulterioară. Multe dintre soluţiile embedded actuale necesită utilizarea unui FPGA pentru a implementa funcţii specifice care nu sunt disponibile pe miezurile microcontrolerelor utilizate. Prin miezul ARM disponibil pe FPGA, Actel oferă proiectanţilor flexibilitatea de a combina aceste funcţii într-un singur cip, cu economisirea spaţiului necesar şi a costului. Aceasta se poate dovedi o opţiune foarte atractivă în aplicaţii importante.

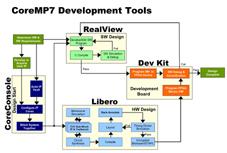

Actel a realizat o întreagă serie de unelte de dezvoltare pentru proiectarea cu CoreMP7. Cheia către acestea o reprezintă CoreConsole. Această nouă unealtă oferă o interfaţă grafică intuitivă şi uşor de utilizat, care facilitează implementarea rapidă a altor IP blocks şi a unui subsistem în jurul procesorului. Constând din două componente – unealta IDP (IP deployment platform) propriu-zisă şi un IP vault – CoreConsole suportă integrarea unor funcţii de temporizare şi UART cu Actel DirectCores, atât la nivelul IP vaults cât şi la IP blocks definite de utilizator.

CoreConsole permite utilizatorilor să reducă timpul de dezvoltare al sistemului şi să realizeze o evaluare a acestuia. Subsistemele periferice – incluzând interfaţă AHB, interfaţă APB, punte AHB-to-APB, controler memorie, controler de întreruperi, temporizatoare, interfeţe seriale şi I/O bufferizate – sunt configurabile în cod RTL ca parte a IDP.

Uneltele software pot furniza drivere şi alte fişiere către alte unelte de dezvoltare de software, permiţând dezvoltarea mai rapidă a programelor care rulează pe miez: acestea pot fi realizate, depanate şi gestionate printr-o versiune de ARM RealView Developer Kit destinat special utilizării cu CoreMP7.

Lansarea CoreMP7 reprezintă un important punct de cotitură, atât pentru industria FPGA cât şi pentru piaţa sistemelor de procesare embedded. Prin combinarea dintre o platformă FPGA configurabilă, sigură, economică financiar şi energetic, cu liderul miezurilor de procesoare, ARM şi Actel au reuşit punerea în practică a procesării pe 32-biţi chiar şi în aplicaţiile embedded cele mai sensibile la preţ. Totodată, prin integrarea funcţiilor de procesor şi subsistem într-o platformă similară ASIC, proiectanţii vor putea trece la următorul nivel de integrare – rezultând o reducere a costurilor – păstrând aceeaşi valoare din punct de vedere calitativ.

de Mike Thompson, Manager, IP Marketing, Actel

www.actel.com