Aplicațiile embedded care necesită performanțe ridicate de procesare a semnalelor digitale (DSP) nu numai că solicită o creștere a performanțelor pentru a putea face față creșterii complexității algoritmilor matematici, ci necesită și adăugarea de caracteristici de comunicație, siguranță funcțională și management. Această combinație de factori conduce la schimbări în modul în care puterea de procesare este implementată în microcontrolerele de înaltă integrare și controlerele de semnal digital.

Aplicațiile embedded care necesită performanțe ridicate de procesare a semnalelor digitale (DSP) nu numai că solicită o creștere a performanțelor pentru a putea face față creșterii complexității algoritmilor matematici, ci necesită și adăugarea de caracteristici de comunicație, siguranță funcțională și management. Această combinație de factori conduce la schimbări în modul în care puterea de procesare este implementată în microcontrolerele de înaltă integrare și controlerele de semnal digital.

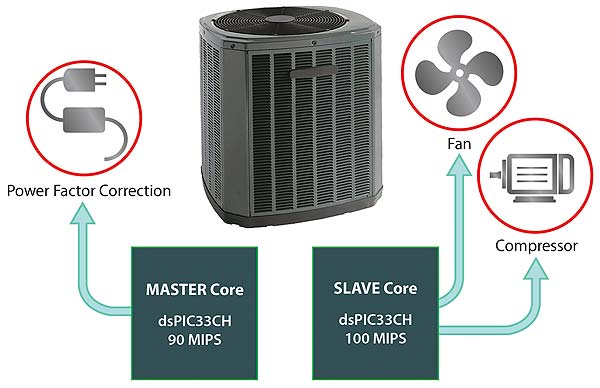

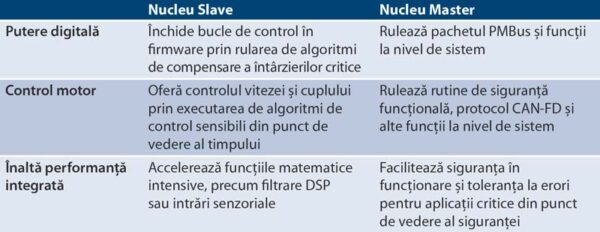

Un exemplu reprezentativ este un proiect de sursă de alimentare avansată. Implementările de astăzi nu fac apel doar la un control precis și eficient al conversiei de energie prin algoritmi matematici și control PWM în timp real. Ele necesită, de asemenea, conectivitate pentru a oferi status operațional în timp real și pentru a primi comenzi de la unitatea de management la nivel de sistem utilizând protocoale precum PMBus. Similar, într-un controler de pompă sau ventilator din industria auto, comunicația printr-un protocol precum CAN-FD (Controller Area Network Flexible Datarate) este necesară pentru comenzi, monitorizare sistem și raportare date de diagnosticare. O unitate de aer condiționat poate avea cerințe chiar și mai complexe, cu sarcini orientate DSP separate pentru a suporta corecția factorului de putere în sursele sale de alimentare principale, precum și control al motorului în buclă închisă în unități de ventilatoare și pompe.

În principiu, un nucleu CPU de mare viteză, prin secvențiere temporală, rulează mai multe fire de execuție (thread-uri) independente, pentru a manipula sarcini de control în timp real cu latență redusă și sarcini de management de rețea și sistem. Cu toate acestea, un nucleu care este proiectat să atingă performanțe atât de mari în orice tehnologie de proces dată poate fi sub nivelul optim în termeni de consum de putere și complexitate.

O altă problemă pentru orice aplicație de timp real rulând pe un singur nucleu este cât de ușor thread-urile și manipulatorul de întreruperi vor respecta termenele de finalizare respective. Ca la orice implementare de partajare a resurselor, un motiv de atenție îl reprezintă durata de timp în care un thread dat va fi blocat de la rulare de către un proces irelevant sau de către un manipulator de întreruperi. Pentru a garanta că un thread va respecta termenul de timp de finalizare în toate condițiile în care thread-urile nu au interdependențe, algoritmii conservativi utilizați pentru a calcula cantitatea de spațiu de trecere (headroom) necesară vor solicita păstrarea unei porțiuni relativ semnificative de cicluri de procesare nealocate.

Există, de asemenea, aspectul general al comutării frecvente a sarcinilor care trebuie luat în considerare, precum și impactul său asupra procesării. Având un număr mare de evenimente de întreruperi pe un singur nucleu, sarcina generală de gestionare a întreruperilor și sarcinile de comutație asociate pot fi semnificative.

O opțiune este de a genera mai mult headroom pentru a obține performanță prin viteze de ceas mai mari. În practică, poate avea mai mult sens divizarea aplicației pe mai mult decât un nucleu de procesor. Pentru orice aplicație multisarcină (multitasking) care nu este dependentă de trecerea unei singure linii de execuție (single thread), utilizarea paralelismului conduce adesea la o eficiență energetică mai ridicată, un determinism mai mare și o dezvoltare mai ușoară.

Implementarea cu două nuclee poate partaja mai eficient sarcina de lucru a unui sistem multisarcină. Aceasta poate, de asemenea, conduce la a fi capabilă să utilizeze frecvențe de ceas de nucleu mai mici, ceea ce poate fi o mai bună potrivire pentru memoriile flash, reducând sau eliminând numărul de stări de așteptare (stall cycles) pe durata cărora procesorul trebuie să aștepte instrucțiuni sau date pentru a reveni de la o solicitare de preluare.

În unele aplicații, natura apropiată a sarcinilor care manipulează surse de date înrudite este favorabilă unei singure secvențe pipeline (Pipeline este o tehnică de creștere a numărului de instrucțiuni ce pot fi executate într-o unitate de timp, fără a ridica viteza ceasului). Dar atunci când se execută funcții diferite în aplicații embedded de înaltă performanță, utilizarea a mai mult decât un singur nucleu are sens, deoarece diferitele funcții nu sunt cuplate între ele.

De exemplu, într-o sursă de alimentare, în care bucla de control închisă este implementată în firmware, performanța este predominant determinată de timpul necesar pentru conversia unui eșantion analogic în digital, calcularea unui nou factor de umplere din această informație și apoi actualizarea PWM. Cu un controler multi-nucleu, este posibilă asigurarea că această funcție critică de timp de întârziere nu este împiedicată de alte activități de sistem prin rularea sa pe un alt nucleu care nu are alte sarcini prioritare de îndeplinit. În paralel cu calculele buclei de control critice din punct de vedere temporal, un alt nucleu CPU poate fi însă însărcinat cu alte responsabilități precum comunicație PMBus și funcție de monitorizare sistem. Similar, într-o aplicație de control al motorului, împărțirea procesării buclei de control și a pachetului de interfață CAN pe diferite nuclee asigură o comutație sigură și precisă pentru motor.

De exemplu, într-o sursă de alimentare, în care bucla de control închisă este implementată în firmware, performanța este predominant determinată de timpul necesar pentru conversia unui eșantion analogic în digital, calcularea unui nou factor de umplere din această informație și apoi actualizarea PWM. Cu un controler multi-nucleu, este posibilă asigurarea că această funcție critică de timp de întârziere nu este împiedicată de alte activități de sistem prin rularea sa pe un alt nucleu care nu are alte sarcini prioritare de îndeplinit. În paralel cu calculele buclei de control critice din punct de vedere temporal, un alt nucleu CPU poate fi însă însărcinat cu alte responsabilități precum comunicație PMBus și funcție de monitorizare sistem. Similar, într-o aplicație de control al motorului, împărțirea procesării buclei de control și a pachetului de interfață CAN pe diferite nuclee asigură o comutație sigură și precisă pentru motor.

Există și un alt avantaj al împărțirii procesului în termeni de timp de dezvoltare a proiectului. Cu toate acestea, este important ca cele două nuclee să fie omogene pentru a putea beneficia de acest avantaj. O opțiune tradițională pentru multiprocesare era de a diviza sarcina de lucru în acord cu tipul procesului. Programul de procesare a semnalului ar trebui să ruleze pe o linie optimizată pentru opțiuni de acumulare multiplă, dar cu puțină abilitate de a rula eficient programul de control în vreme ce un procesor de uz general are grijă de rutinele cu numeroase ramificații. În practică, în numeroase aplicații de timp real, aceasta este o arhitectură cu care se lucrează dificil. Operațiile de procesare a semnalului depind adesea de condiții externe, care se pot schimba rapid. Comunicațiile de inter-procesare, care au nevoie să își sincronizeze stările pe diferite nuclee pot fi complicat de implementat deoarece impun cerințe de timpi de sincronizare mai mici decât mesajele utilizate pentru a lega comenzile și actualizările de stare la o interfață de rețea.

Există și un alt avantaj al împărțirii procesului în termeni de timp de dezvoltare a proiectului. Cu toate acestea, este important ca cele două nuclee să fie omogene pentru a putea beneficia de acest avantaj. O opțiune tradițională pentru multiprocesare era de a diviza sarcina de lucru în acord cu tipul procesului. Programul de procesare a semnalului ar trebui să ruleze pe o linie optimizată pentru opțiuni de acumulare multiplă, dar cu puțină abilitate de a rula eficient programul de control în vreme ce un procesor de uz general are grijă de rutinele cu numeroase ramificații. În practică, în numeroase aplicații de timp real, aceasta este o arhitectură cu care se lucrează dificil. Operațiile de procesare a semnalului depind adesea de condiții externe, care se pot schimba rapid. Comunicațiile de inter-procesare, care au nevoie să își sincronizeze stările pe diferite nuclee pot fi complicat de implementat deoarece impun cerințe de timpi de sincronizare mai mici decât mesajele utilizate pentru a lega comenzile și actualizările de stare la o interfață de rețea.

Arhitecturi unificate de controler de semnal digital, precum dsPIC33 de la Microchip rezolvă problemele de sincronizare prin aducerea celor două comportamente de execuție împreună, într-o singură arhitectură. Pe o asemenea linie se pot desfășura cu mare viteză operații matriciale și de acumulare multiplă, dar se oferă și capabilitate de ramificare rapidă și răspuns rapid la întreruperi, astfel încât parametrii și algoritmii se pot adapta din zbor la schimbarea condițiilor. Acest lucru simplifică implementarea software de algoritmi complecși de procesare de semnal. Totuși, presiunea pe timpii de proiectare, înseamnă că trebuie să se facă față unor provocări legate de integrare de program, indiferent de arhitectura aleasă. În numeroase aplicații, combinația între comunicație și funcționalitatea de control este adesea împărțită între echipele de dezvoltare, fiecare dintre acestea fiind specializate în zona sa.

O problemă cheie a integrării programului de la două sau mai multe echipe este de a determina cum vor opera între ele programarea și prioritizarea sarcinilor. Se pare că decizii mici, precum prioritatea unei sarcini individuale pot avea un impact major asupra aplicației de timp real. O asemenea (mică) decizie va putea însemna că sarcini vitale vor fi blocate în a avea acces la procesor pentru perioade mai lungi decât este dorit pentru bune performanțe. Având seturile de sarcini distribuite pe două procesoare, inginerii cu cele mai multe cunoștințe despre prioritățile relative ale thread-urilor pe care le folosește aplicația, sunt responsabili de stabilirea priorităților respective.

Împărțirea procesării permite, de asemenea, gestionarea și alocarea mai ușoară a memoriei de date și siguranța că setul de instrucțiuni makefiles și setările linker-ului pe care le-au creat și depanat în timpul proiectului rămân pe loc în pachetul software final. Acest lucru reduce suprasarcina echipei de integrare software și reduce durata până la lansarea pe piață a produsului.

Cu toate că împărțirea procesării ajută deja la optimizarea efortului de dezvoltare și fluxului de procesare, Microchip continuă să aducă îmbunătățiri structurale pentru creșterea performanțelor. Un exemplu în cazul dsPIC33CH cu nucleu dublu este implementarea unui număr crescut de regiștri selectați în funcție de context, cu scopul de a îmbunătăți răspunsul la întreruperi. În noul nucleu dsPIC33CH sunt, de asemenea, implementate instrucțiuni suplimentare pentru a crește performanța DSP.

Fiind un controler de semnal digital (DSC), dsPIC33CH include un număr de periferice avansate, cu scopul de a reduce costul și dimensiunea sistemului. Acestea includ convertoare de mare viteză ADC și DAC cu generare de formă de undă, comparatoare analogice, amplificatoare analogice cu câștig programabil și generatoare PWM de înaltă rezoluție (până la 250ps). Funcțiile avansate, precum mai multe periferice inteligente și un periferic generator trigger ajută la reducerea numărului de întreruperi la nivelul nucleului într-o aplicație de sursă de tensiune sau de control al motorului. De exemplu, UART-urile oferă suport hardware pentru LIN/J2602, IrDA®, DMX și extensii pentru protocol smart card, cu scopul de a reduce încărcarea pe software. În mod asemănător, perifericele CAN-FD includ un procesor al fluxului de biți și retransmitere automată programabilă pentru a le permite să ruleze cu mai multă autonomie față de nucleul CPU.

Fiind proiectat pentru a răspunde cerințelor de dezvoltare ale echipelor de ingineri de astăzi, dsPIC33CH de la Microchip este optimizat pentru aplicații de control embedded din lumea reală, cu performanțe ridicate și timpi critici. Arhitectura vine în sprijinul clienților care solicită “proiectare separată, integrare fără probleme”. Rezultatul este o arhitectură care crește performanța, în vreme ce reduce durata de lansare pe piață a produsului, dimensiunea sistemului și costul.

Autor: Markus Wimmer,

Business Development Manager, Unitatea de business microcontrolere pe 16-biți

Microchip Technology | https://www.microchip.com