Cum să îndeplineşti de pe acum cerinţele cipurilor din deceniul următor

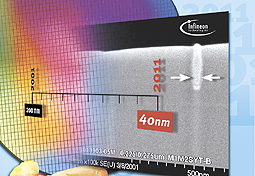

Munich , 14 mai, 2001 – Infineon Technologies anunţă că centrul său de cercetare Munich Corporate Research Labs a demonstrat că dispune deja de tehnicile necesare pentru a realiza interconectări de circuite integrate ce pot fi folosite pentru generaţiile viitoare de cipuri, ce se extind până la intervalul de timp 2011-2014 !

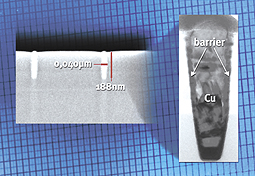

Cercetătorii de la firma Infineon au reuşit să producă trasee metalice cu o lăţime de numai 40 … 50nm, cuprinse în şanţuri dintr-o peliculă dielectrică folosită pentru izolarea electrică a traseelor conductoare. Astfel de linii metalice foarte înguste sunt folosite pentru cele mai scurte conexiuni electrice dintre tranzistorii de pe cip.

Noile “fire” de legătură au fost supuse unei evaluări electrice, şi s-a verificat că rezistenţa electrică este suficient de scăzută pentru toate lungimile de conexiune relevante. Evaluarea demonstrează efectiv că pentru procesul (ce continuă neîntrerupt) de reducere a dimensiunii cipurilor, nici fabricarea unor asemenea linii ultra-înguste, şi nici rezistenţa electrică serie nu vor fi obstacole de netrecut.

Astăzi, nu există încă instrumentele de microlitografie (mai corect ar fi nano-litografie) necesare pentru fabricarea generaţiilor viitoare de cipuri, prevăzute pentru intervalul de timp 2011-2014. Infineon a depăşit această problemă folosind o tehnică cu distanţier pentru a îngusta deschiderile măştii folosite pentru transferul configuraţiei pe stratul subţire de dielectric. Aceasta deschide calea pentru fabricarea unor structuri cu dimensiuni laterale mult sub dimensiunile critice care pot fi realizate actualmente pe cele mai avansate echipamente de fabricaţie pentru litografie.

Realizarea firmei Infineon demonstrează şi posibilitatea de extindere a tehnicii de damaschinare, abordarea de vârf folosită în industria semiconductoare pentru a produce topologii avansate de metalizare a cipurilor. În această tehnică, se realizează şanţuri şi găuri care se umple prin depunerea de metal pe placheta semiconductoare, urmată de o îndepărtare completă a întregii cantităţi de metal ce acoperă structurile umplute, prin “lustruirea” chimică şi mecanică. Îndepărtarea prin şlefuire fină este posibilă deoarece metalele folosite pentru interconectare, fie ele cupru, aluminiu sau aur, au duritatea mai mică decât dielectricii (oxid sau dioxid de siliciu, nitrură). Tehnica aceasta indirectă a fost numită damaschinare, după metoda prin care odinioară se aplicau ornamente fine pe săbiile de Damasc.

Plăcile de siliciu (la IPRS foloseam denumirea de <

Respectivul consorţiu multinaţional format din cei mai avansaţi fabricanţi de semiconductoare din lume are în Austin o facilitate de producţie pentru dispozitive cu dimensiunea critică de 250nm, ceea ce este actualmente foarte bine, dar nu chiar “cel mai bine” pe plan mondial – aţi văzut în ziar ştiri referitoare la producţia de serie mare din Taiwan a componentelor cu trasee de 0,15 microni …

Rezultatele obţinute de cercetarea firmei Infineon arată că tehnologiile actuale de interconectare pe cip pot fi folosite până la încheierea “hărţii mondiale de tehnologie pentru industria semiconductoare (International Technology Roadmap for Semiconductors =ITRS), care se întinde până în anul 2014. Iniţiativa ITRS descrie cerinţele tehnologice şi de materiale pentru generaţiile viitoare de cipuri.

www.infineon.com

Ing. Cristian Malide