FPGA de 10K – 40K porţi cu microcontroler AVR şi 36K × 8 SRAM

Specificaţii generale

• Conţine un FPGA de tip AT40K bazat pe logică configurabilă de tip SRAM şi un microcontroler de mare performanţă cu nucleu AVR RISC 8 biţi;

• Zona de FPGA:

– 4,6K – 18,4K biţi de celule SRAM distribuite cu acces monoport / dual port;

– structură optimizată pentru aplicaţii DSP;

– se poate reconfigura dinamic;

– consum de putere extrem de redus;

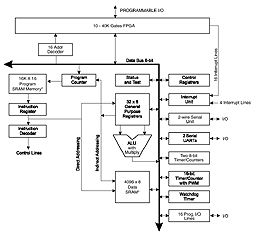

• Microcontrolor AVR RISC de 8 biţi:

– peste 120 de instrucţiuni puternice, majoritatea cu execuţie într-un tact;

– instrucţiune de înmulţire hardware;

– performanţă de peste 30 MIPS;

– arhitectură internă optimizată pentru utilizarea de compilatoare C (32 × 8 registre acumulatoare);

– moduri multiple de economisire de putere (Low Power Idle, Power Save, Power Down).

• 36K × 8 SRAM pentru instrucţiuni şi date alocabili dinamic:

– până la 16K × 16 SRAM de instrucţiuni, timp de acces = 15ns;

– până la 16K × 8 SRAM de date, timp de acces = 15ns.

– interfaţă serială standard pe 2 fire;

– 2 interfeţe seriale UART;

– 2 timer / counter de 8 biţi cu prescaler separat şi PWM;

– 1 timer / counter de 16 biţi cu prescaler separat, mod comparare, mod captură şi PWM dual de 8, 9 sau 10 biţi.

• Legătura AVR – FPGA:

– 16 linii de la microcontroler merg direct la FPGA;

– librărie FPGA cu diverse periferice;

– 16 întreruperi de la FPGA la AVR.

• Circuite oscilatoare multiple:

– Watch Dog Timer cu oscilator integrat;

– oscilator pentru microcontroler cu frecvenţă selectabilă software;

– oscilator pentru circuitul timer / counter pentru implementarea de RTC (= Real Time Clock).

• Software integrat pentru PC cu suită software ce include şi co-verificarea între tona de FPGA şi cea de AVR.

Descriere

Seria AT94K, FPSLIC, este o combinaţie între un circuit FPGA de tipul AT40K şi un microcontroler cu nucleu AVR RISC de 8 biţi. Microcontrolerul dispune de cantitate mare de SRAM pentru date şi instrucţiuni, conform specificaţiilor generale de mai sus. De notat că, datorită faptului că instrucţiunile rezidă în celule SRAM cu acces de 15ns, acest lucru permite microcontrolerului să aibă viteză mare de lucru fără complicaţii tehnologice costisitoare. Conţinutul memoriei SRAM de la microcontroler se încarcă, odată cu memoria de configurare FPGA, de asemenea de tip SRAM, imediat după RESET dintr-o memorie externă nevolatilă. Se poate folosi o memorie cu acces paralel sau cu acces serial, cum ar fi AT17K.

Zona de FPGA are, după cum am amintit mai sus, logică de configurare de tip SRAM. Faptul că FPSLIC deţine logică de configurare SRAM, iar memoria de instrucţiuni şi de date a microcontrolerului AVR este tot de tip SRAM, prezintă unele avantaje faţă de implementările de FPGA cu memorie de configurare nevolatilă. Memoria SRAM este mai ieftină şi mai rapidă. În plus, circuitele de acest tip au de regulă capsule complicate cu mulţi pini ceea ce face ca manevrarea celor ce au memorie de configurare nevolatilă de pe programator pe placa de aplicaţie să fie dificilă şi periclitabilă de erori de operator. FPSLIC au memorie de configurare SRAM şi pot fi lipite direct pe placa de aplicaţie. Drept memorie nevolatilă de configurare se foloseşte de regulă un AT17K, o memorie serială Flash de configurare, disponibilă în 8 pini.

Memoria de configurare SRAM mai permite şi reconfigurarea parţială sau totală a FPSLIC-ului în timpul funcţionării, fără pierdere de date. ATMEL a numit acest proces Cache Logic.

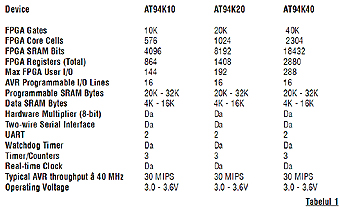

În tabelul 1 se prezintă seria AT94K cu principalele caracteristici, iar în figura 1 arhitectura internă.

Microcontrolorul AVR RISC de 8 biţi integrat în FPSLIC este capabil de 1MIPS / MHz; această putere de procesare se obţine cu consum redus de putere, nucleul AVR fiind recunoscut ca având cel mai bun raport putere / consum în familia microcontrolerelor de 8 biţi.

Nucleul AVR dispune de 32 de registre de 8 biţi de uz general, legate direct la unitatea logico-aritmetică. Astfel, 2 registre diferite se pot comporta în cadrul unei instrucţiuni ca şi 2 acumulatoare, adică operaţia logico-aritmetică implicând un registru sursă şi un registru destinaţie se execută într-un singur tact.

Setul de instrucţiuni al nucleului AVR este deosebit de puternic, eficienţa codului scris fiind de circa 10 ori mai mare decât codul scris pentru microcontrolerele CISC, la aceeaşi frecvenţă.

Familia FPSLIC este susţinută de pachetul software “System Designer” ce oferă şi scule de co-verificare între zona FPGA şi zona AVR.

Tradus de Cristian Alexe

ALEXE ELECTRONICE AE S.R.L.

Tel. / Fax : (01) 323.91.45

e-mail: calexe@canad.ro

www.atmel.com

www.codico.com